Cadence推出最新版本OrCAD Capture V16.6,新增New Function

1.Close All Tabs、Lock Reference,SI Analysis更可在SigXplorer设定的

拓朴结构及 Constraints 可直接回编到电路图上,大幅简化与缩短Pre-Sim 的作业流程。

2. Configuring Menus and Toolbars(自定义菜单和工具栏):

自定义 Menu 和Toolbars。如:改变Menu item 位置和名称等。

文件位置shareorResources

3.修改XML File,未保存页面会标示*

Enhanced Save Function for Design and Library:

修改过的Design or Page or Library 会在未Save 前,标示Mark(*)星号。

4. Enhancements in the Find Function(增强了查找功能):

Ⅰ Property Name=Value:可指定找寻某一个Property 的Value,Ex:pcb footprint=PLCC28

Note:Property name 需為完整字串,万用字元(*)只支援Value 字串。

Ⅱ Regular Expressions:搜寻区间范围的零件,Ex:U4[1-4]

Note : 当两个功能都被开啟时,Regular Expressions 搜寻只支援Property Value 的字串。

Ⅲ Global Replace for OffPage:

一次性替换相同Net Name 的OffPage,将A 名称换成B 名称。

5. Enhancements in Cache Updates(增强Cache的更新):

可在Design Cache 中一次选取多个零件,透过Replace Cache 换成同一个零件。

6. Setting the User Assigned Flag:

Ⅰ. Preserve Designator:当Reference 清成”?”时,同类型复合式零件可保留Section。

Ⅱ. Preserve User Assigned Valid References:可以保留User 自订的Reference。

註:保留Part Reference 可透过

1.Edit Property

2.直接修改Part Reference Value

3.从PCB Board 修改完后Back Annotate 回线路图

Preserve Designator(保留原本的Section)

Preserve User Assigned Valid References(修改过的Reference 会加上( _ )底线)

7. Design Level Auto Reference:

在阶层式电路中摆放零件时,可依照整份Project 自动编号,避免零件编号重复。

8. Browsing Designs Created Using Earlier Versions:

可直接View 旧版本的线路图,当执行存档动作时,才会跳出警示讯息是否要Update Design。

9. Closing all Tabs:

可以利用菜单或是在分页上,选择一次关闭所有开啟的Page 或是关闭所有Page 但保留当前view 的这一页。

10. Design Rule Check (DRC) Enhancements:

可以透过TCL/TK 编写客製的DRC 检查。

11. Project Save As Enhancements

对於Project 的Save as 除了OPJ 档外,现在能把DSN 或是Output File 一併存入指定的资料夹中。

12. Enhancements in the NetGroup Use Model:

Assign a NetGroup to a Bus:

可以在 BUS 线上,直接放上NetGroup 名称

13.Reorder Pins in an Unnamed NetGroup:

可针对 Unname NetGroup 裡的成员调整顺序。

14.Add and Remove Pins from a NetGroup:

NetGroup Block pin 脚,可直接从NetGroup 中选择要接的NetGroup 及不想接的。

15.Visible NetGroup References:

现在不论Port 或是Offpage 也能清楚辨识属於哪一个NetGroup。

16.Find NetGroup References:

可以利用Find 功能寻找NetGroup Pin。

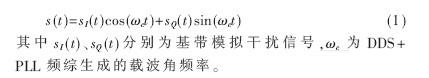

OrCAD Capture V 16.6 正式支援连动SigXplorer 进行讯号完整性分析作业

以往RD或 SI 工程师若要进行 Constraint 规范的制订时 , 往往必须使用 SigXplorer或进行

Pre–Simulation . 但是要进行此操作必须请 PCB Layout 工程师来协助作业 , 相当不方便.

由16.6 版开始 , Capture正式支援与SigXplorer可直接双向连动作业. RD或SI工程师要进行

Constraint 规范评估与设定时不需要再去麻烦PCB Layout 工程师 , 我们可由线路图直接產生电路拓

朴结构并带入到SigXplorer 环境中进行讯号完整性的分析。

工程师在分析完毕后可在SigXplorer 裡面设定 Constraint 后再回编到 Capture .

当 PCB Layout 工程师在 netin 完成后 , 这些 Constraint 设定也随著 netlist 的导入而自动带到

Allegro / OrCAD PCB Layout 的 Constraint Manager 环境中.

且尔后当该份电路图被再次利用时 , 工程师无须再去重复先前的作业 , 所有的拓朴结构 , T 点 , Xnet

及 Constraint 资料都已经存在电路图上.

Analyze / Edit Topology

SI Model Association

Topology Extraction

Netlist to

PCB Editor

Topology Association

Audit / Refine Topology & Constraints

PSpice16.6新功能列表

1. 使用操作改进与提升

软件本身提供Leaning PSpice学习教程

快速调用PSpice元器件

PSpice模型加密支持256-bit AES加密算法

新增PSpice仿真元件库

支持IBIS模型到PSpice模型导入

新增What-if设计流程

Model Editor支持隐藏引脚原理图符号导入

2. 核心功能改进与提升

仿真精度提高,支持64位数据精度

仿真收敛性大大增强,提供了众多可供用户选择的设置

仿真速度提升,支持多核运算

I/O优化,增强PSpice处理大数据量波形文件能力

3. Tcl支持与集成

FSP16.6新功能列表

1. 直接调用已有的PCB设计文件,利用FSP来重新设计或重复使用PCB文件中FPGA部分。

2. 新增滤波,匹配电路需要的电阻,电容等。

3. 可以整体添加设计中所有电源管脚的退耦电容。

4. 在Allegro下面也可以自动换pin。

5. 调入FSP数据后新增各种自动换pin形式,使FPGA设计变得更加高效简单。

6. 新增文档对比功能,用户可以根据文档比较来确认管脚交换前后的改动。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多