在基于FPGA的SOC设计中,常使用串口作为通信接口,但直接用FPGA进行串口通信数据的处理是比较繁杂的,特别是直接使用FPGA进行串口通信的协议的解释和数据打包等处理,将会消耗大量的FPGA硬件资源。

为简化设计,降低硬件资源开销,可以在FPGA中利用IP核实现的嵌入式微处理器来对串口数据进行处理。

本文中的设计采用了XILINX的FPGA,可选用的嵌入式微处理器IP核种类繁多,但基于对硬件资源开销少的考虑,终选用了Picoblaze。

嵌入式微处理器PicoBlaze适用于Spartan-II/E、CoolRunner-II和Virtex系列FPGA,运行速度可达到40MIPS以上,提供49个不同的指令,16个寄存器,256个地址端口,1个可屏蔽的中断。其性能超过了传统的8bit微处理器。嵌入式微处理器Picoblaze的功能、原理见参考文献[1]。

Picoblaze使用灵活,但其缺点是可寻址的存储空间非常有限,因此为满足实际需要本文同时也提出了使用片外SDRAM器件对其存储能力进行扩展的设计方法。

2 串口收发接口设计

2.1串口收发接口硬件设计

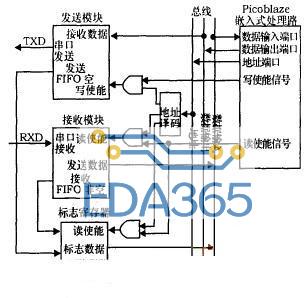

嵌入式微处理器PicoBlaze本身并不具备串行接口,因此必须在FPGA中设计串口接收和发送模块并通过总线结构与Picoblaze连接。

串口接收和发送模块的设计可采用成熟的IP核。实际设计中采用了XLINX的串口收发IP核,其特点是串口波特率,符号规则都可以灵活地定制,同时具有16字节的接收FIFO和16字节的发送FIFO。

使用Picoblaze和串口收发IP核构成的串口收发系统结构见图1。

在设计中,发送模块、接收模块和标志寄存器分别有不同的地址,Picoblaze通过地址端口对串口收发模块进行访问。设计中的标志寄存器,可用于指示发送模块和接收模块中FIFO的状态,Picoblaze通过查询标志寄存器来完成对串口数据的收发控制。

2.2串口收发接口软件设计

串口发送、接收子程序

Picoblaze通过对标志寄存器的查询,根据FIFO的状态进行操作。串口发送和接收子程序流程见图2。

Picoblaze的编程,类似于汇编语言。

串口发送子程序代码如下:

(1)串口接收子程序

receive:

INPUT s0,uartrxflag ;查询接收FIFO是否非空

AND s0,01

AND s0,s0

JUMP Z,receive ;若FIFO为空时继续查询

INPUT rxdata,uartrx ;若FIFO非空时读取数据

RETURN

(2)串口接收子程序

translate:

INPUT s0,uarttxflag ;查询发送FIFO是否为空

AND s0,01

AND s0,s0

JUMP NZ,translate ;若发送FIFO非空时继续查询

OUTPUTtxdata,uarttx ;若发送FIFO为空时写入数据

RETURN

协议处理子程序

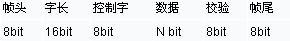

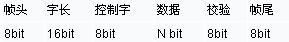

本文应用中的串口通信,采用应答机制,数据具有一定的帧结构,Picoblaze需要对命令帧进行拆包处理,并根据帧的内容进行相应的操作,然后发送响应帧。

表1 通信数据的命令帧结构

表2 通信数据的响应帧结构

根据帧格式,Picoblaze对串口数据的处理流程见图3。

以上的Picoblaze程序流程所处理的数据帧结构是较为简单的,当需要处理复杂的通信协议时可以考虑采用多个Picoblaze并行处理。

3 存储器接口设计

Picoblaze的优点是资源占用少,使用灵活,但可寻址的地址空间多为256字节,无法满足对大量通信数据进行存储的需要。因此本文中采用了SDRAM器件来对Picoblaze的存储能力进行扩展。

SDRAM器件的管脚分为控制信号、地址和数据三类。通常一个SDRAM中包含几个BANK,每个BANK的存储单元是按行和列寻址的。SDRAM的具体特性见参考文献[3]。

SDRAM在使用时需要专用的控制器来产生满足SDRAM所需的信号。FPGA中SDRAM控制器也有多种IP核可以选用。出于对设计通用性的考虑,本文中采用了一款Altera提供的SDRAM控制器IP核,并增加了必要的设计以满足与Picoblaze的接口要求。SDRAM控制器IP核的功能、原理见参考文献[4]。

对Picoblaze与SDRAM控制器的接口设计有以下几个出发点:

总线匹配

Picoblaze为8位处理器,数据线仅8bit,而SDRAM控制器总线宽度与SDRAM相同,可以为8、16或32bit。因此对于SDRAM控制器的数据Picoblaze必须以字节为单位进行处理。

地址控制

Picoblaze地址线仅8位,无法直接对SDRAM进行寻址。因此Picoblaze对SDRAM的寻址可借鉴先入先出存储器FIFO的设计,即设计专门的地址计数器,通过地址计数器实现对SDRAM的寻址。

时序匹配

Picoblaze的运行速度不超过40MHz,而SDRAM的工作速度通常大于100MHz。因此为了满足SDRAM的时序要求,要增加必要的缓冲机制。

3.1存储器接口硬件设计

Picoblaze与SDRAM存储器接口的硬件原理框图见图4。

控制状态机控制的地址计数器为SDRAM控制器提供地址,同时控制状态机还控制输入数据缓冲区和输出数据缓冲区,并且根据Picoblaze的地址端口数据和读/写使能信号产生SDRAM控制器的命令字。

(1)SDRAM初始化

每次加电或复位后控制状

(2)数据写入SDRAM

输出数据缓冲区由16×8bit的FIFO构成,当Picoblaze向输出数据缓冲区写入超过8个字节后,通过“半满”信号使控制状态机进入SDRAM的长度为8的突发写模式,在写入完成后控制状态机将地址计数器增加8,以准备好下的写入。

(3)数据读取

数据读取时Picoblaze首先向控制状态机发送读取请求,控制状态机进入SDRAM的长度为1的突发读模式,并将读取的数据写入输入数据缓冲区,此后Picoblaze再由输入数据缓冲区中读取数据。在读取后,地址计数器做相应的增加,以实现先入先出功能。

以上的设计方法适用于需要数据连续写入后再连续读取的场合。

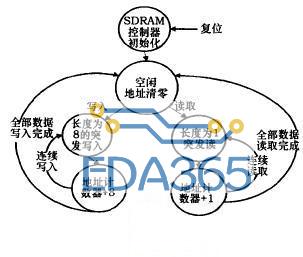

控制状态机状态图见图5。

3.2存储器接口软件设计

由于在SDRAM控制器与Picoblaze之间增加了控制状态机,简化了Picoblaze的程序设计。

(1)数据写入

数据写入时Picoblaze向输出数据缓冲区直接写入数据即可。

(2)数据读取

数据读取时Picoblaze首先向控制状态机发出请求,然后等待输入数据缓冲区的数据准备就续后再读取。

4 结论

本文在XILINX FPGA中采用嵌入式处理器Picoblaze进行SOC设计,以较少的硬件资源实现了对串口通信数据的处理,同时采用SDRAM器件对Picoblaze的存储能力进行扩展。所采用的设计已应用于多个产品中。经过了长期的使用和测试证明文中的设计方法稳定、可靠,并且具有资源占用少,设计灵活的优点。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多