高速电路设计中的信号衰减是让人头疼的一件事,作为电路设计工程师在布线时应该降低信号衰减。本文主要介绍高速电路设计中降低信号衰减方法,希望对你有所帮助。

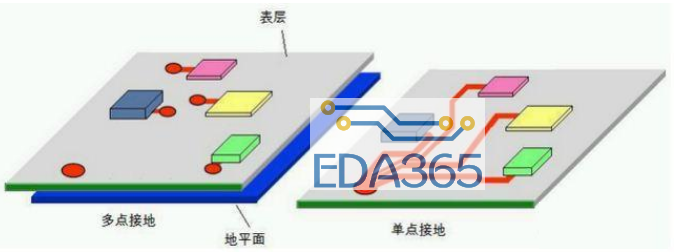

一、降低电抗路径

在高速电路设计中,将接地层分为数字部分和模拟部分,但应将这两个部分连接在靠近电源的地方,以便提供一条短的电抗路径。同时,将电路接地通孔栅栏放置在高速电源平面周围会产生良好的抑制效果,因为它会产生两个异相辐射器。

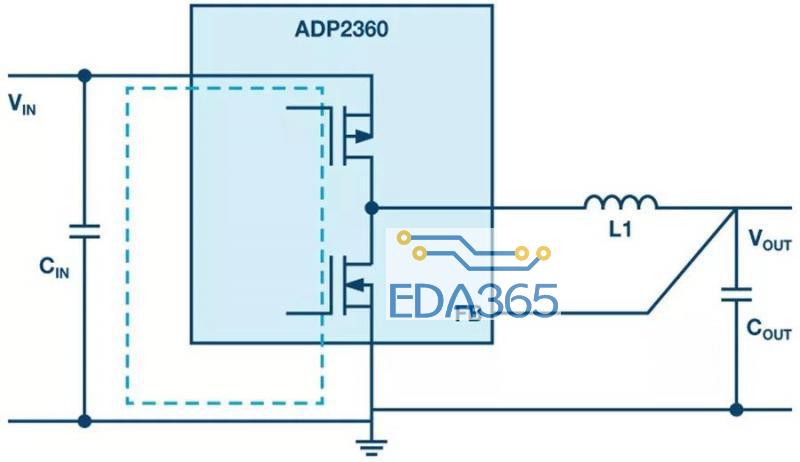

二、保证电源完整性

高速电路设计时加一个高速地,这样防止模拟电路和数字电路对高速电路部分产生干扰和辐射。如果层数允许,将高速电源平面放置在两个接地平面之间,这将使板上的高速电源平面和接地平面分离。

三、确保阻抗一致性

在高速电路设计中,由于高速信号会在较短的走线上产生传输线效应,因此较好使高速走线尽可能短。在电路板上使用阻抗控制,以确保走线在整个电路板上具有一致的阻抗。

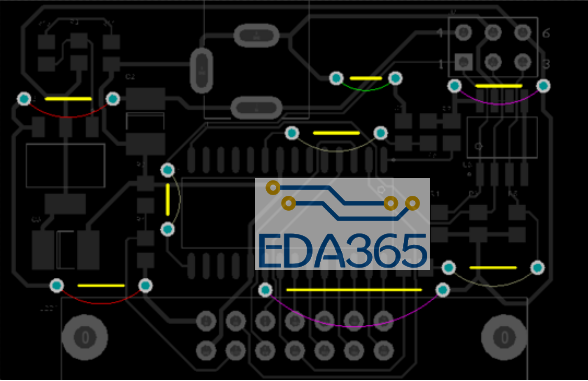

四、注意过孔

高速电路设计时,以尽量降低使用过孔数量。因为每个通孔都会给走线增加阻抗,而设计通孔以使其具有与走线匹配的特定阻抗非常困难。应该对任何通孔进行反钻,以防止信号共振,并且应格外小心,以确保差分对上的反钻是对称的。如果必须要在高速走线上使用过孔,选择是并行使用两个过孔以防止阻抗变化。这样有两个好处,1、它降低了走线上的附加阻抗;2、并联的两个通孔的总阻抗降低,从而增加了通孔对信号的低谐振频率。

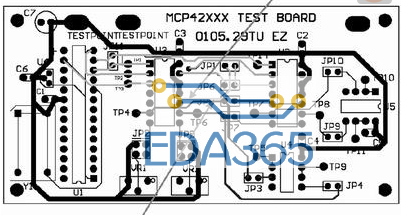

五、使用表面贴装元件

高速信号设计时,使用表面贴装元件。因为使用通孔组件,则元件引脚上的剩余部分会产生另一个信号反射源,从而引起信号衰减。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多