PCB制造过程中最常见的错误之一是层次顺序不合适,这可能导致整个过程失败。 PCB装配过程可以从电气的连续性角度起作用,甚至可以通过电气检查。在设计中,平面与信号层的顺序以及相邻层之间的距离是很重要的。

为了保证生产所需的信息以正确执行层处理的视觉检查,PCB设计人员需要将正确的铜特征设计到制造数据中,即可以实现适当的层叠次序。而这些铜特征会提供检查最终组件的机制,一旦进行内部Q&A检查就会被清理到制造所。

层识别?

添加到每个层上的铜的第一个功能就相对于所有其他层标识层顺序。每个层接收一个层号,直接蚀刻到铜中,这表示其在层叠中的位置,层编号必须包含在成品板的区域内。层数应位于板的边缘附近,以免干扰电路的电气特性。它可以在每个层上采用单个数字的形式。但是,这些数字可能并不堆叠在一起。当所有检查图堆叠,从上往下查看检查图时必须清楚可见。

为了更容易识别,层数通常放置在矩形框内。从层数周围的区域中取出焊接面罩和丝网功能,以便于通过完整的PCB通过放置在组件后面的检查光源观察层数。层数不能连接到任何层上的铜功能,如电源层或多边形。

每一层的铜几何体上蚀刻的层数

显示目视检查用焊料掩模去除的层数

PCB堆叠和测试轨线?

堆叠的条纹和测试迹线的边缘视图

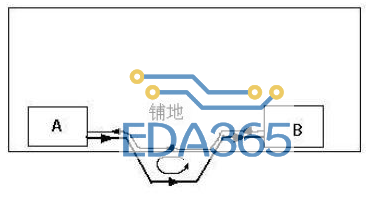

PCB堆叠是在PCB边缘的铜特征,以便于层次顺序的视觉检查。当PCB从面板布线时,几何形状必须延伸到板边缘外部,以露出铜。通过观察成品板边缘的堆叠的条纹,可以看到适当的叠层几何形状。

测试轨线的目的是验证叠层中每个层上的后蚀刻铜厚度和宽度。测试迹线的长度为50mil,厚度为5mil,并且必须在板边缘外延伸,以便当PCB从面板布线时露出铜。测试痕迹的边缘视图可以用检查显微镜来测量。该功能在具有阻抗驱动几何形状的设计中是至关重要的。

在薄膜层上绘制条纹尺寸和测试迹线

注意:堆叠的条纹和测试轨线不能连接到任何平面上的电源平面或多边形等铜特征。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多