今年的闪存峰会,东芝奉上不少干货。

除了获得展会最佳的XFMEXPRESS形态固盘、以太网SSD、XL-Flash等,东芝在路线图中还前瞻了SAS 4接口、PCIe 5.0/6.0标准、甚至是BiCS第四、第五代、第六代、第七代闪存产品,信号带宽分别高达800MT/s、1200MT/s、1600MT/s和超过2000MT/s。

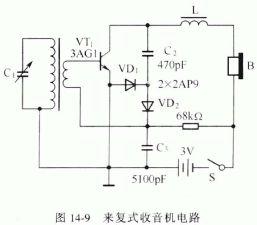

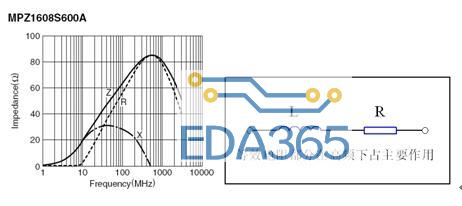

同时,5bit/cell的PLC(Penta-level cell)闪存也新鲜登场,存储密度比QLC更高,但对主控、电路设计的要求也更高。如图所示,PLC闪存需要主控准确控制32路电压,挑战相当大。

与MLC、TLC相比,QLC(4bit/cell)已经相当慢,并且读写寿命最低。不过,东芝表示,NVMe协议中的新功能如ZNS(分区命名空间)应该有助于缓解其中的一些问题。ZNS设计之初是用于减少写入放大,减少过载和DRAM高占用,当然,也能提高吞吐量和改善延迟。

另外,从工艺上,东芝也在研发分割式3D存储工艺,看起来似乎是可以拼接QLC和PLC,以增加容量密度。

APP下载

APP下载 登录

登录

热门文章

热门文章