摘要:近年来,由于设计复杂度的增长,对于验证提出了更高的要求。验证环境变得越来越大,越来越复杂,设计和验证的双重压力导致仿真变得越来越慢。所有验证/仿真的速度已经成为当前SOC设计进程中的重大挑战。

在我们的项目中,我们使用Synopsys的验证flow以及近年来Synopsys提供的新的方法/工具,比如性能分析工具来分析仿真瓶颈,使用分块编译来加速编译,使用并行多核技术来加速编译/运行。使用UVM来增加环境的可复用性,等等,这些技术/特性的引入都大幅度加速了我们的仿真速度并减少了仿真时间。

项目以及验证环境介绍

我们的项目是GPU的项目,对于仿真性能有较高的要求,所以在项目中希望使用尽可能多的新技术来缩短仿真时间以及加速验证。

我们的验证环境使用UVM标准库来搭建的。验证环境如图1所示。

使用了Synopsys公司的VCS来作为我们的仿真工具。

工具版本:VCS 2012.09-SP1,Verdi 2013.04

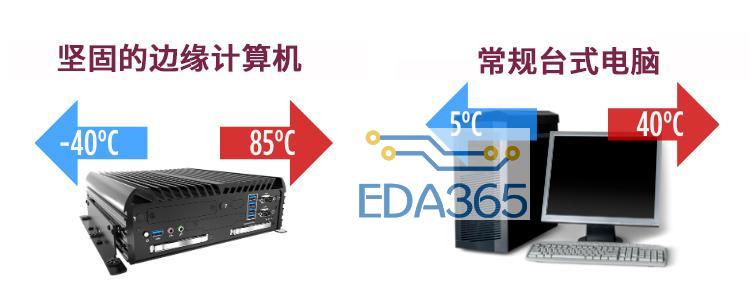

硬件环境如表1所示。

加速编译的方法

随着电路规模的不断变大,编译时间也成为了仿真过程中重要因素,如何加快/重用编译数据库,是加速整个仿真过程不可缺少的部分。VCS提供了很多好的技术来加速编译过程。

并行编译

当前基本上我们的服务器都能提供多核支持,并行编译选项可以使用服务器的多核来提供更快的并行处理,来快速编译生成数据库。VCS并行编译的选项如下:

-j[no_of_processes]

比如 vcs –j4 …,注意no_of_processes的数目不要超过实际可以提供的物理核数目。

APP下载

APP下载 登录

登录

热门文章

热门文章