小型快速的流式视频系统结合采用微型H.264核和赛灵思ZynqSoC

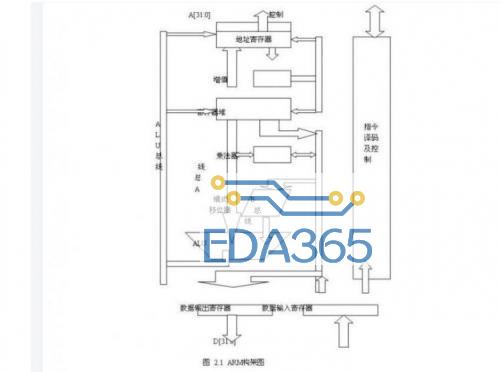

ASSP架构不灵活,而基于FPGA微处理器组合的系统虽然尺寸大但较为灵活,一直以来设计人员为创建PCB占位面积小的基于IP的流式视频系统,除了在这两者之间反复权衡外别无他选。将软核微处理器集成到FPGA,就无需单独的处理器和DRAM,但最终系统的性能可能无法与以外部ARM处理器为核心且可能还包括USB、以太网及其它有用外设构建的解决方案所提供的性能相媲美。随着赛灵思Zynq-7000AllProgrammableSoC和小型H.264核的问世,现在仅用一组DRAM就可在超小型PCB板上构建出一个具有用多条高速AXI4总线连接起来的ARM双核和高速外设所实现的高性能的系统(见图1)。

虽然针对FPGA的H.264核问世已有相当长的一段时间,但至今仍没有一款H.264核够快够小,能够达到足以转换1080p30帧视频的水平,而且仍旧适用于小型低成本器件。将A2eTechnologies公司的最新微型H.264核与ZynqSoC结合使用,可构建一种低时延系统,该系统能够以15~60fps的不同帧速率对720p~4K之间的多种视频流进行编/解码。将A2eTechnologiesH.264核集成到ZynqSoC器件中,可大幅缩减板级空间并明显减少组件数,同时在ZynqSoC集成ARM双核还可避免使用单独的微处理器及其必须连接的存储体。

APP下载

APP下载 登录

登录

热门文章

热门文章