摘要:介绍了一种最新DDR NAND闪存技术,它突破了传统NAND Flash 50 MHz的读写频率限制,提供更好的读写速度,以适应高清播放和高清监控等高存储要求的应用。分析该新型闪存软硬件接口的设计方法。

关键词:DDR NAND;NAND Flash;1080P;嵌入式接口

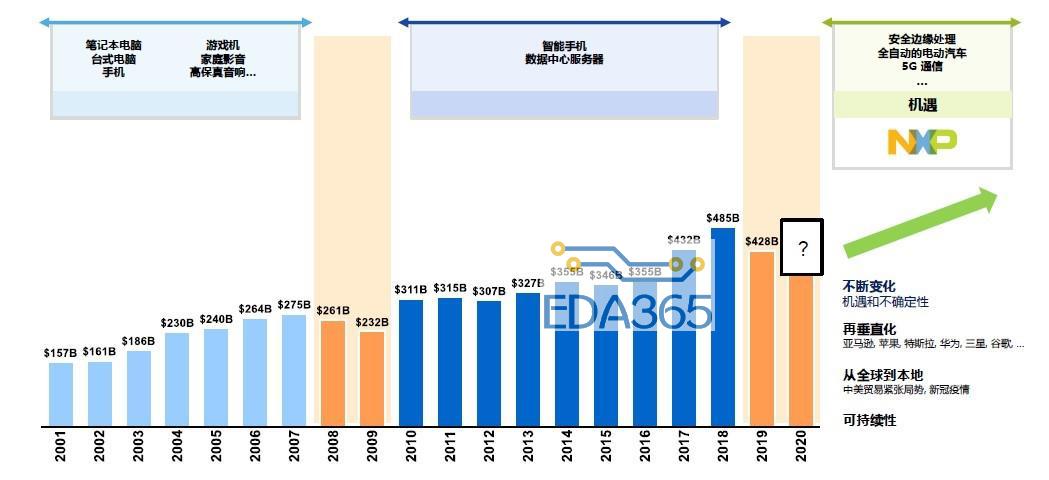

随着Android手持多媒体电子消费产品的风行,高画质监控系统的普及,1080P全高清支持已成为各种多媒体设备未来占领市场的必备武器,目前许多产品对1080P实时解码已突破并实现,但在1080P实时编码方面还是寥寥无几,其中一个重要因素是带宽太大,当今流行的嵌入式存储设备NAND Flash已以达到要求。在此情况下,存储器生产商开发出新一代闪存设备DDR NAND。

1 DDR NAND闪存的特性

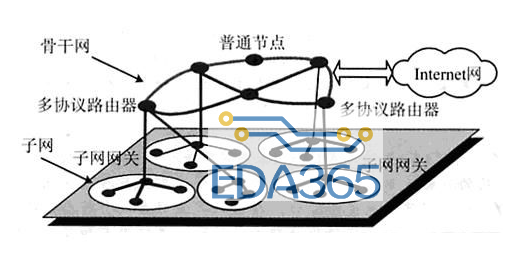

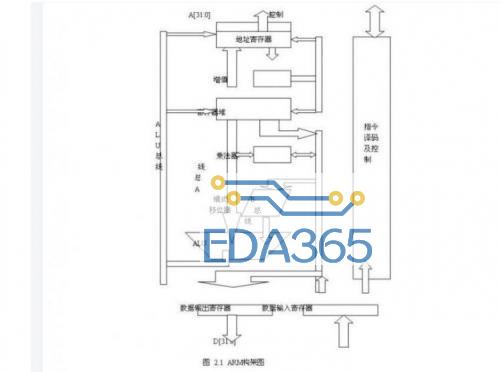

与传统的48脚NAND Flash引脚定义不同,DDRNAND闪存不再分别划分读时钟(RE#)和写时钟(WE#),而是将读写合为1个时钟,即CLK,而用W/R引脚的高低来区分这次是读操作还是写操作,如图1所示。数据I/O接口也改为正负双沿采集的DQ数据线。如图1中DDR NAND闪存部分所示,各引脚功能说明如下:

CE1#~CE4#:片选信号,低为使能。一个48脚的物理NAND Flash片子最多能同时包含(封装)4个NAND Flash。

CLE:命令锁存使能信号,高为使能。

ALE:地址锁存使能信号,高为使能

CLK:时钟信号。

W/R#:区分读写操作信号,高为写,低为读。

DQ0~DQ7:数据/地址/命令复用数据线。

R/B1#~R/B4#:NAND状态信号线。

VCC,VCCQ:接电源。

VSS,VSSQ:接地。

R:无定义。

APP下载

APP下载 登录

登录

热门文章

热门文章