硬件描述语言Verilog为数字系统设计人员提供了一种在广泛抽象层次上描述数字系统的方式,同时,为计算机辅助设计工具在工程设计中的应用提供了方法。该语言支持早期的行为结构设计的概念,以及其后层次化结构设计的实现。这在设计过程中,进行逻辑结构部分设计时可以将行为结构和层次化结构混合起来;为确认正确性还可以将描述进行模拟,并提供一些用于自动设计的综合工具。因而Verilog语言为设计者进行大型复杂数字系统的设计提供了途径。超大规模集成电路设计的典型流程如图1所示。

本文将以顺序状态逻辑有限状态机的设计为例介绍用Verilog语言设计数字电路的一般过程。

1 设计规范与设计构思

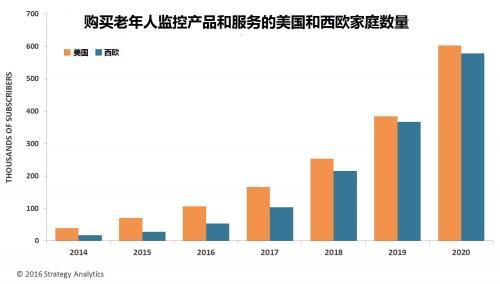

电子设计工程师在设计过程中不可避免地会遇到设计可执行特殊操作序列电路的工作,如用来控制其他电路进行操作的控制器,而有限状态机(Finite Status Machine,FSM)是设计这种能执行特殊操作序列电路的一种非常有效的模型。FSM的结构通常由当前状态寄存器、下一状态逻辑和输出逻辑三部分构成。FSM也有很多种模型,本文仅以顺序状态逻辑FSM的设计为例来说明用Verilog进行集成电路设计的一般设计过程。为简单起见,本设计只设计了包含有8个状态的顺序状态逻辑FSM。8个状态分别为One、Two、ThreeA、ThreeB、ThTeeC、Dummy、Four、Five。开始状态为One,各状态之间的转换关系如图2所示。

该顺序状态逻辑FSM的功能及要求如下。

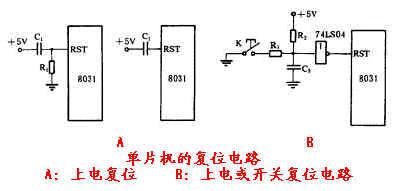

(1)同步复位信号Reset至少要维持4个时钟周期的高电平信号,以保证状态机进入状态One。

(2)当状态机在5个状态中循环时,A、B、C 3个输入按优先级使状态机从状态Two进入相应的状态ThreeA、ThreeB、ThreeC、Dummy。

(3)复位后,如果A持续为高电平,则输出信号Y1的周期为时钟周期的5倍,且高电平维持的时间为1个时钟周期。

(4)如果A、B维持为低电平,而C维持为高电平,则输出信号Y3的周期为时钟周期的5倍,且高电平维持的时间为1个时钟周期。

(5)如果A维持低电子,而B维持高电平,则输出信号Y2与Y1和Y3不同,只维持1个时钟周期的高电平。因为当状态机进入状态ThreeB时,信号BeenInState3B被设置为1,而该信号就会禁止状态机再次进入状态ThreeB,直到另一个复位信号出现为止。

以上是一个时序电路的设计,如何保证正确的时序是设计的关键。根据设计要求,该状态机至少应该有8个端口:5个输入端口(A、B、C、Reset、Clock),3个输出端口(Y1、Y2、Y3)。其中输入端A、B、C和Reset信号均由时钟边缘进行触发,Reset具有最高的优先权,而输入信号A、B、C的优先权则依次递减。

该顺序状态逻辑有限状态机的端口示意图和设计构思图分别如图3和图4所示。

2 用Verilog语言编写源代码

APP下载

APP下载 登录

登录

热门文章

热门文章