目前针对嵌入式系统开发的调试工具品种繁多,如ARM公司的AXD debugger软件与Mutil-ICE仿真器等。但是大部分嵌入式调试工具价格过高,因此设计实现一种速度快、性能稳定、价格低廉、易于实现的ARM调试工具是十分必要的。

1 ARM JTAG调试原理

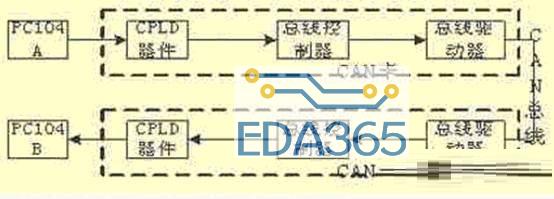

ARM典型的调试系统结构如图1所示。调试系统包括调试主机、仿真器和调试目标。

调试主机是一台运行调试软件(例如ADS)的计算机。调试主机可以发出高层的调试命令,例如设置断点、访问内存等[2]。

仿真器用来将调试主机发出的高层调试命令转换为底层的ARM JTAG调试命令。因为目标机无法识别调试主机发送来的高级命令,因此就需要仿真器将调试主机发出的高层调试命令转换为底层的ARM JTAG调试命令[3]。在整个调试系统中起到重要的作用,其性能也决定了整个调试系统性能。

2 方案设计

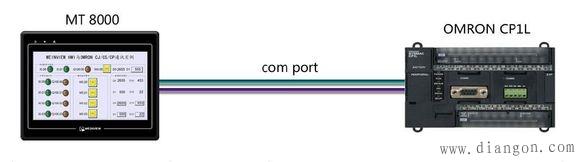

本文提出了一种采用PHILIPS公司的ARM7芯片LPC2148设计,具有USB2.0通信方式、高速稳定的ARM仿真器实现方案,如图2所示。

守护进程接收从IDE集成开发环境发送来的调试命令,将其通过USB总线转发到ARM仿真器,ARM仿真器再将调试命令转换成JTAG格式的信号并发送到I/O口,从而控制调试目标执行特定的操作,达到调试的目的。同理,从调试目标返回的数据,先经过ARM仿真器的译码,再经过守护进程返回到IDE开发环境,从而形成一个完整的调试系统。

3 硬件电路设计

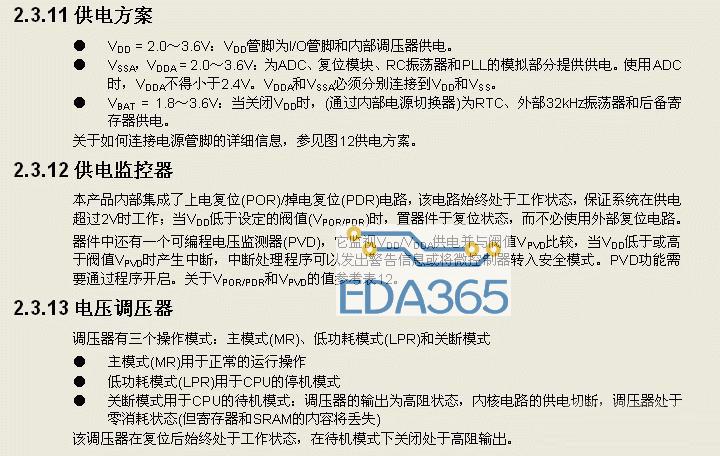

本设计的最大特点是采用了LPC2148作为主控芯片。该芯片内部集成了ARM7TDMI-S微控制器和完全兼容USB2.0的设备控制器,支持32个物理(16个逻辑)端点;支持控制、批量、中断和同步端点;所有端点都有一个双向的DMA通道。因为芯片内部集成了USB控制器,大大降低了电路板的设计难度和开发成本。其硬件电路框图如图3所示。

(1)本机JTAG调试电路

为了便于调试和烧写程序,将芯片LPC2148的JTAG接口接到一个20引脚的标准JTAG插口。本设计中使用引脚P0.8、P0.9、P0.10、P0.12、P0.14作为外部JTAG接口,尽量不用有其他接口功能的引脚,如P0.11、P0.14接口与I2C接口SCL1、SDA1功能复用,以便于将来的硬件升级。为了增强带负载能力,使用一片74HC244芯片,同时为了尽量兼容大部分ARM开发板上的不同JTAG插口,本设计提供了一个20引脚的JTAG插口和一个14引脚的JTAG插口。

APP下载

APP下载 登录

登录

热门文章

热门文章