翻译自——eetimes

IBM对其前沿商用处理器Power9进行了升级。这些芯片是为最先进的超级计算机和最苛刻的数据中心工作负载而设计。IBM表示,Power9的性能是Power8的1.5倍,这得益于该公司能够设计出的最先进的I/O子系统技术。接下来是TechInsight的技术评估,它深入研究了Power9的一个版本的工作原理。

IBM为Power9采用了一种新的微架构,如14 nm FD-SOIFinFET,结合了用于eDRAML3高速缓存的深沟电容,这使得eDRAM单元阵列、SCE等性能得到了改善,也具有非常低的延迟,并保留了性能规格。IBM的目标是将下一代Power10缩小到10 nm甚至7 nm,以获得更多的性能改进和更低的延迟。

本文总结了TechInsights对IBM 14HP HKMG FD-SOIFinFETeDRAMcell架构、流程和设计的分析,这些分析最近在IBM Power9处理器中使用。

IBM Power9 02CY297 FC-PLGA组件由一个NIMBU52C处理器芯片和用于L3缓存的eDRAM块组成,由Global Foundries (GF)制造。深沟电容(DTC)和SOIeDRAM单元设计,取代了SRAM,这是IBM Power和System-z处理器上高密度和高性能高速缓存存储器的核心解决方案之一;然而,最近的14HP DTC SOIeDRAM电池设计与之前的22nm SOI技术有很大的不同。

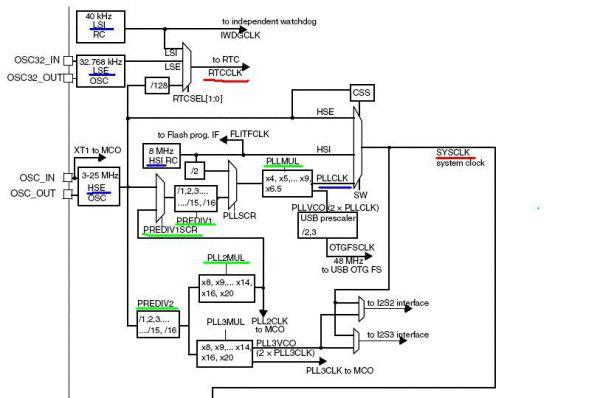

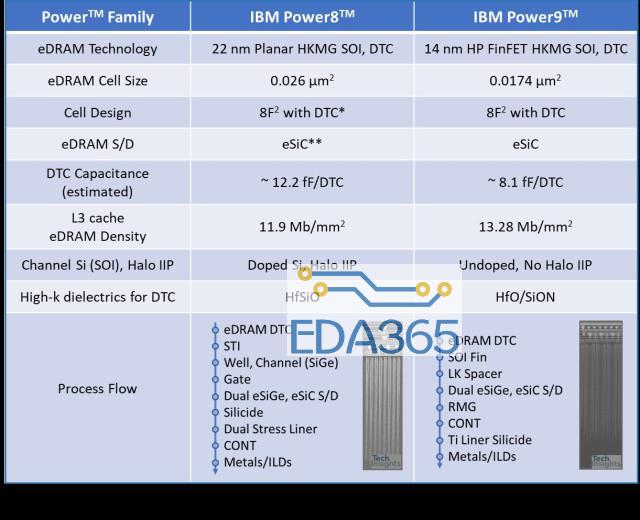

次图显示了IBM的DTCeDRAM技术节点和单元大小的最新趋势。自从在45nmeDRAM中首次引入DTC结构以来,IBM/GF已经采用并采用了对eDRAM(DTCeDRAM或DTeDRAM命名)缓存区域的DTC结构。IBM Power8 22 nm DTCeDRAM单元由SOI/BOX和Gate -first HKMG组成,而IBM Power9 14 nm DTCeDRAM单元采用FinFET+ HKMG RMG(替换金属门)门禁(WL)设计。

DTCeDRAM技术节点和单元大小的最新趋势。

TechInsights对IBM Power9处理器的eDRAM进行了分析,并列出了在架构、流程、材料和设计方面GF一系列的创新,

Global Foundriesfabbed14HP FD-SOI

3rd HKMGeDRAM

第一款带有RMG的FinFETeDRAM

第四深沟槽电容器(DTC)eDRAM

用于L3缓存的eDRAM

0174 µm2 SOI DRAM bit cell with 8F2

DTCeDRAMcell capacitance (estimated) ~8.1fF/cell with ULKHfO/SiONhigh-k dielectrics and DTC depth 3.5 µm

采用直接转矩技术生产电池电容器和去耦电容器

eSiGe(PMOS门)的双外延层+eSiGe(PMOS Gates)

共17层金属(不含铝UBM连接层)

64纳米1X M1至M5节距,2X M6至M9节距,以及4X M10和M11节距

ULK介质适用于M1到M9 ILD,而LK ILD适用于M10到M15

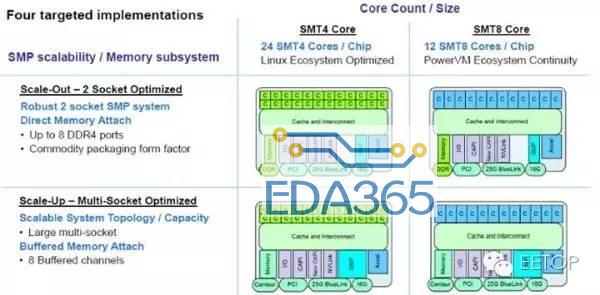

据悉IBM将发布4个Power 9版本。其中的两个版本用了每个内核8线程及每个芯片12内核的结构,可用于IBM 的Power虚拟化环境;另外两个版本用了每个内核4线程及每个芯片24内核的结构,可用于Linux。二者均有2个版本,一个版本用于两插槽8 DDR4 端口服务器,另一个版本用于多芯片、缓冲Dimm型服务器。

多元化的选择有助于吸引OEM商家。IBM 一直在利用OpenPower社群试图鼓励其他商家建造Power系统,OpenPower社群现有200 多个玩家。到目前为止,中国对该社群的兴趣十分大,一家中国合作伙伴正在造自己的Power芯片。

Power 9在有些部件里用了标准DDR4Dimm内存,这可以降低OEM门槛,因为可以将包装商品化从而降低成本。

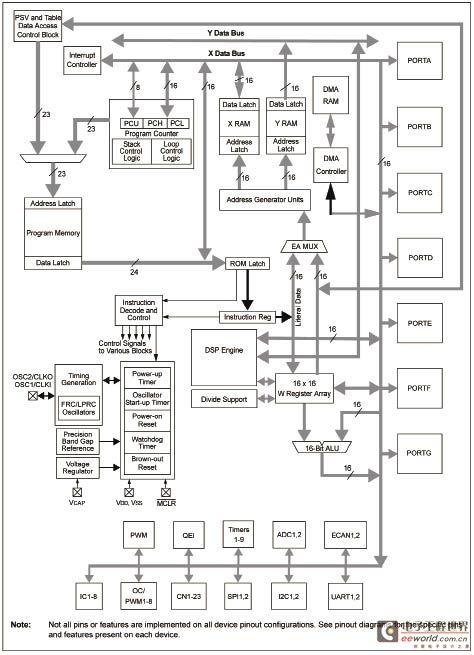

Power9 的 120 MB L3分成 10 MB的块,供两个内核共享

IBM 的BrianThompto在Hot Chip活动上第一次公开介绍Power 9

Power 9 的加速策略或许是该款芯片最有意思的东西。

Power 9是第一个使用了每秒16GTransfer、 PCI Express 第4 代互连的微处理器,而PCI Express 第4代互连的最终规格仍在等有待有关部门的批准。另外,Power 9还用了新的 每秒25 Gbit物理互连,名为IBMBlueLink。

两个互连均支持48个通道,并可容纳多种协议。PCIe 链接利用IBM 的 CAPI 2.0 连接 FPGA 和 ASIC。BlueLink将配置新一代NVLink及新的CAPI。NVLink的开发也可用于Nvidia GPU。

DTC = deep trench capacitor.eSiC= insituedoped epitaxialSi:C(C cannot be detected due to a very low doping level of ~E15/cm3)

深沟槽结构也用于与单元电容器相同尺寸和材料的片上电压供应解耦。DTC高k介电材料选用极薄的HfO层,MIS电容器选用锡。HfO具有很高的介电常数(~25),而薄的锡层可能增加了介质的热稳定性(带隙6.5 eV)和CB偏移。电容器的顶板采用了一种非常适形的5.8 nm厚度锡原子层沉积(ALD)工艺。多晶硅带模式是大量的掺杂和用于连接DTC到访问设备,这与之前的22nmeDRAM的设计相同。

如上表所示,通过比较流程;14 nmFinFETSOIeDRAMvs. 22 nm planar SOIeDRAM。平面SOIeDRAM单元需要通道掺杂和光晕注入,而14nmFinFETFD-SOIeDRAM单元不需要它们,即14HPeDRAMcell通道未掺杂。栅极氧化物、TiAlC/ tin基WF层和TiAlO/W栅极填料被集成用于有源鳍上的eDRAM访问栅极。

这个表总结了BEOL Cu金属层、节距和固体层的情况。IBM Power9处理器模具总共由17个金属层组成,使用了所有Cu材料,比之前的15个增加了2层。IBM Power8 Cu金属层使用80 nm 1X路由M1到M5, 1.8X路由M6到M7,而IBM Power9 metal层使用64 nm 1X M1到M5, 2X路由M6到M9。M1设计缩减了20%。每一层BEOL ILD都采用了SiOF-based LK andSiOC-based ULK材料。

延伸阅读——IBM POWER系列处理器的前世今生

Power是Power Optimization With Enhanced RISC的缩写,是由IBM开发的一种RISC指令集架构(ISA)。

IBM的很多服务器、微型计算机、工作站和超级计算机都采用了Power系列微处理器。Power芯片起源于801 CPU,是第二代RISC处理器。在1990年,Power 芯片被RS或RISC System/6000 UNIX工作站(现在称为 eServer 和pSeries)所采用。从Power 3开始以及之后推出的Power系列微处理器都采用的是64位PowerPC架构。

801的设计非常简单,但是由于所有的指令都必须在一个时钟周期内完成,因此其浮点运算和超量计算(并行处理)能力很差。Power体系结构就着重于解决这个问题。Power芯片采用了100多条指令,是一个非常优秀的RISC体系结构。

PowerPC,最初的含义却不是Power,而是Performance Optimized With Enhanced RISC;PC指的是Performance Computing。目前,主流的PowerPC处理器制造商有IBM、Freescale (原摩托罗拉半导体部,现已与NXP合并)、AMCC、LSI(已被Avago收购)等。其中以IBM和Freescale的PowerPC处理器最为流行。IBM的PowerPC家族IBM目前共有3个主要的Power系列:Power、Power PC和CELL。POWER,POWER PC中间,还有一个Star系列。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多