1 系统整体方案及硬件设计

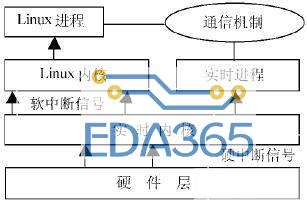

系统要求在FPGA片内利用SoPC技术实现便携式的图像采集与处理。它通过对原始图像的扫描,经数字图像处理与识别后即可将得到的大容量的承载信息(包括文字、头像、指纹等个人信息)在LCD上显示,并可通过USB接口将信息拷贝,或通过RS-232接口将信息上传给PC机,也可以通过GPRS将获得的信息方便快捷地发往数据中心作验证。

整个系统的核心部分是内嵌Nios II软核的FPGA,外围设备和芯片包括图像获取设备、显示器及片外SDRAM和FLASH存储器、输入设备等。系统结构框图如图1所示。

系统的工作过程是:系统配置完成后,视频获取设备获取视频图像,每帧图像经模数转换生成图像数据进入预处理模块,经预处理后的图像数据送入SDRAM存储器,由Nios II处理器进行图像的后续处理和控制。处理后的图像经数模转换在监视器上实时显示。

1.1 图像采集接口电路设计

本系统采用美国OmiVision公司的数字式彩色CMOS图像传感器OV7640。该芯片分辨率为640×480像素,成像速度为30帧/s,采取逐行扫描方式,输出为数字信号。工作原理如图2。

图像采集的程序流程是:首先Nios初始化OV7640的各个寄存器,主要包括状态寄存器(STA)、数据和时钟控制寄存器(CLKRC)、自动增益控制寄存器(AGC)的设置;然后查询等待,条码图像被OV7640采集进入数据寄存器后,通过DMA方式存入SDRAM,Nios再从SDRAM中提取数据进行译码。

1.2 基于Nios的SoPC系统硬件设计

基于Nios软核的SoPC系统设计是整个系统硬件设计的核心,包括Nios软核处理器的设计、数据采集控制的设计、图像信号FFT分析的实现、参数显示以及RS232通信模块的设计等。另外,使用Nios进行嵌入式设计在硬件上必需使用Altera公司的FPGA。

Nios处理器核的硬件设计是根据系统的功能要求定制合适的CPU和外设,然后在SoPC和Quartus II中实现。在硬件设计流程中,可以灵活定制Nios CPU的许多特性甚至指令,可以使用Altera提供的IP Core来加快设计者开发Nios外设的速度并提高外设性能,也可以使用第三方的IP Core,或者使用VHDL、Verilog自行定制外设。

系统Nios外设主要包括:

(1)CMOS图像传感器接口模块。由于Altera没有提供CMOS图像传感器接口模块,所以使用VHDL编程自行定制。通过VHDL编程设计一个CMOS图像传感器控制模块,采用接入Avalon总线的方式自定制外设。

(2)由于要对数字图像信号进行FFT运算,所以采集的数据必须先进行存储,然后再作FFT计算。因此,必须设计FIFO存储器和FFT实现的硬件。[page]

(3)RS232通信电路模块。RS232通信可以通过串行口UART加上一个转换芯片来实现。所以,本系统利用SoPC中提供的UART组件来实现RS232通信接口的设计。

(4)LCD液晶显示模块。LCD液晶显示是通过配置Nios的PIO接口来控制的。

除上面所述之外,根据系统要求,Nios处理器核应当配置以下组件及接口模块:cpu、boot_rom(用于系统引导)、uart1(用于系统的仿真调试)、uart_rs232(用于串口通讯)、Timer1(系统内部时钟)、lan_timer(以太网通信用时钟)、button_pio(用于参数设置)、lcd_pio(用于参数显示)、user_logic_ad_nv_ctl和user_logic_ad_power_ctl(自定义的AD转换的接口模块)、Ethernet(用于以太网通信)、ext_ram(外部SRAM)、dma(用于将采集的数据直接存入SRAM中)和ext_flash(外部flash)。

本系统中数据的存储是通过设计FIFO存储器电路实现的。FIFO存储器电路主要由一个双口RAM模块(Dual-Port RAM)和状态机模块(State Machine Table)组成,通过先进先出(FIFO)堆栈把数据存储在双口RAM中。其设计是在Matlab环境下利用Altera DSP Builder设计工具实现的。

电路设计完成并仿真验证成功后,应用DSP Builder中的signal Compiler进行编译分析,经signal Compiler转换后可以变成VHDL语言的程序。同时,在Quartus II中,可以将VHDL语言程序转换成电路符号,便于应用原理图的方法设计硬件系统。由FIFO存储器的VHDL程序生成的电路符号如图3所示。在设计过程中,需要用到Quartus II软件和其内嵌的IP Toolbench。按照本系统的要求设置FFT的参数为:点数为1 024点,数据宽度为12 bit。最后设计生成FFT的MegaCore Function模块,包含一些VHDL程序及其他相关的文件。由VHDL程序生成的FFT模块电路符号如图4所示。

2 系统软件设计

系统软件部分包括实时操作系统μC/OS-II和数据采集与处理部分的应用程序。在Nios II IDE中将软件开发分为两大部分,一部分是底层系统软件的开发,主要完成BSP(板级支持包)的功能;另一部分则是用户应用软件的开发(包括用户硬件驱动及用户上层应用软件)。整个用户软件的开发及调试工作都可以在Nios II IDE中完成。

2.1 实时操作系统μC/OS-II在Nios上的移植

在本课题中使用的是μC/OS-II的v2.83版本,源码可以从Micrium的网站上获得。同时还要从网站上获得μC/OS-II在EDK中使用的配置文件μCOS-II_v2_1_0.mld和μCOS-II_v2_1_0.tcl。将这两个文件放到EDK能找到的路径下,这样在EDK中才能配置使用μC/OS-II。在EDK中通过菜单Software->Software Platform. Settings打开配置窗口,在OS中选择μC/OS-II,OS Version中选择 v2.83a,然后进入OS & Library对μC/OS-II进行配置。

在Nios II IDE中,可以对μC/OS-II的源码位置、BSP包源码位置、移植程序文件位置、应用程序文件位置进行修改,同时还可对μC/OS-II进行剪裁配置,如是否使用事件、互斥信号量、消息邮箱及任务是否可删除等。

2.2 实时操作系统下的软件设计

μC/OS-II在ALTERA的Nios微处理器上移植并测试完成后,建立了基于μC/OS-II实时多任务内核的硬件开发平台,但μC/OS-II仅是一个有源码的内核,在实际应用中,对外设的操作需要自行编写底层的代码。在此平台下进一步开发,实现数据采集功能,需要建立相关的应用程序,也就是要根据整个系统的要求,划分不同的任务,这些任务交由实时内核来调度管理。一般一个任务对应于一段独立的主程序,它可能调用各种子程序,并使用各种系统资源,以完成某种特定的功能,并且实时内核允许多个任务并行运行。采用实时操作系统,使应用程序的编写简单且易于调试。

主程序用C语言编写,其主要程序如下:

void main()

{sys_initialize();//系统初始化

while(1)

{ad_fft_ctl();//数据采集及FFT计算子程序

case collection_order: //图像采集命令

image_collection();//图像采集

image_process();//图像处理

image_save();//图像保存

mps_decoder();//调用相应的解码算法

case rs232_transfer://传输数据命令

lcd_display(p1,p2,p3);//LCD液晶显示子程序

}

}

3 系统调试与应用实例

调试包括硬件和软件调试。硬件调试分析电路的设计合理性及焊接工艺的可靠性,以保证所设计的各个模块合理,重点放在调试自己所设计的IP核和硬件逻辑的可靠性与适用性。软件调试主要是集中在系统内核的应用程序,以保证各个功能都成功实现。这是一个相当复杂的过程。[page]

3.1 系统硬件调试

为了验证FPGA能否正常工作,把CMOS图像传感器的输出连接到Nios II开发板的扩展插座上,编写VHDL程序,读取CMOS图像传感器的输出并存储到FPGA的内部RAM中,利用Quartus II的工具In-System Memory Content Editor,读取内部RAM的值。

要设计用户逻辑或者外设,除了要编写实现特定功能的逻辑之外,还要编写与Avalon总线的接口,这就要求对Avalon总线的规范很熟悉。测试结果表明,程序能够通过JTAG接口成功下载到FPGA上,显示在LCD上的运行结果也正确。这说明FPGA、JTAG接口、电源、晶振和LCD显示等电路均能正常工作。

3.2 系统软件调试

Nios II集成开发环境(IDE)是Nios II系列嵌入式处理器的基本软件开发工具,所有的开发任务都可以在Nios II IDE下完成,包括编辑、编译、调试程序和下载。系统的软件设计和调试全部在Nios II IDE下完成,使用C/C++语言编程。

3.3 系统应用实例——PDF417二维条码的识别

二维条码扫描器开始工作时,首先采集二维条码图像数据,由于实际工作中条码图像会出现污损等情况,对码字的正确译出造成影响,所以必须对采集到的图像进行降噪、校正等预处理。条码图像为灰度图像,对其进行二值化才能进行码字识别。在将PDF417码的所有码字正确分割后,以查表方式在码本中查找与码字相对应的值,将编码数据译出。为确认扫描的有效性,必须进行前向错误校验。如出错,则进行纠错。最后,将译码的正确数据传输到上位计算机或LCD显示。识别过程如图5所示。

二维条码数据全部识别完以后,Nois控制输出一个中断申请信号,开始执行中断服务程序。首先选定数据传输口地址,然后译码结果可通过RS-232接口被送至计算机,计算机接收该译码数据后,中断结束。重复该过程,直至全部译码结果输出结束。整个软件处理过程控制在0.3 s以内,完全可以满足系统实时性要求。

本文对基于FPGA以及Nios的图像采集与处理系统设计进行了深入研究,并在设计完成硬件实验平台的基础之上,完成了嵌入式操作系统的移植及应用程序的设计。系统采用Nios处理器和FPGA,必要的外围电路和处理器能集中在一块芯片上,减少了系统体积,简化了系统规模,同时可以方便地进行扩展和升级。μC/OS-II操作系统移植到Nios处理器上,提高了系统的运行效率和可靠性。嵌入式图像处理系统作为一种新型的智能化视觉系统,以其种种优点使之具有广阔的应用前景和良好的经济价值。研究与推广嵌入式图像处理系统无疑是科技进步的表现,尤其当嵌入式图像处理系统应用于工业生产上时,必能提高生产效率,推动生产力的发展

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多