0引言

随着微电子技术的发展,系统集成向高速、高集成度、低功耗发展已经成为必然,同时SoPC技术也应用而生。SoPC将软硬件集成于单个可编程逻辑器件平台,使得系统设计更加简洁灵活。SoPC综合了SoC,PLD和FPGA的优点,集成了硬核和软核CPU、OSP、存储器、外围I/O及可编程逻辑,用户可以利用SoPC平台自行设计高速、高性能的CPU和DSP处理器,使得电子系统设计进入一个崭新的模式。

该设计运用SoPC技术实现嵌入式数字化语音录制与回放。其中,介绍了在FPGA上构建WM8731的I2C总线,以及数字化语音在SRAM中的存储,并利用Matlab7.0.4软件对所采集的语音数据进行仿真。SoPC是现在电子技术、电子系统设计的汇聚点和发展方向。充分体现了其高性能、设计灵活和易用等特点。

1系统整体方案

系统以Altera公司的FPGA芯片(CycloneⅡ系列)EP2C35F672C6NK为平台,结合音频编/解码芯片WM8731实现语音录制与回放。该FPGA芯片具有丰富的片内资源,大量的逻辑宏单元和多个硬件乘法器,大量的自定义I/O接口,此外还有4个锁相环,为系统提供实时时钟。设计中充分利用了FPGA的高速并行和Avalon总线自定义硬件外设的优势,从而构建了一个高集成度、高性能的系统。

语音通过话筒输入,由音频编/解码芯片WM8731以8kHz的A/D采样率转换成16位PCM码缓存。此外,为确保采集的语音数据不丢失,先将语音存储在SRAM中,再作后续处理。整体系统框架图1所示。

[page]

1.1芯片工作原理

音频编/解码芯片WM8731上电后必须将工作模式设置在系统要求的状态下,因此上电后需要用VERILOGHDL编写程序模块对芯片的工作模式进行设置。该语音编/解码芯片有多种工作模式,A/D变换后,语音的采样频率与采样位宽都需要根据系统的具体要求,合理配置。语音芯片的配置时序为I2C模式,芯片接口为主模式,即由WM8731提供位时钟,A/D转换和D/A转换的左、右声道控制相位时钟,以及转换后的数据PCM码输送给FPGA处理器。以下为芯片配置字列表,WM8731内部控制字寄存器有16个,在芯片初始化时,在制作ROM表格中完成。相应的程序设置如下:

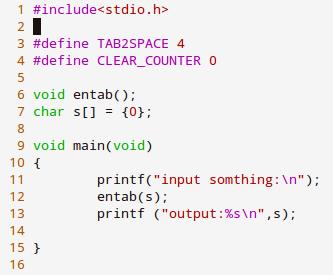

1.2配置单元模块

配置单元模块综合顶层图如图2所示。从程序编译分析报告(见图3)可以得出,该单元模块消耗了101个逻辑单元,它作为语音采集模块的一个子模块。在配置电路中,模块CLOCK_50将输入的50MHz系统时钟分频为1MHz,作为I2C总线模块的工作时钟,CLOCK_50模块中写出的上面程序代码是一个表格,存储了配置的控制字。I2C总线模块的I2C_SDAT和I2C_SCLK是数据线和时钟线,DE2板固定分配了专门的I2C数据线和时钟线的引脚线。

[page]

1.3语音采集模块

语音采集单元顶层综合模块如图4所示。系统通过语音采集模块将语音芯片采集的声音数据串/并转换为16位PCM码,声音数据传送至S-RAM存储器内保存,这里设置了4s录音时间,用户1次输入3个孤立词(如数字),4×8KB=32KB,考虑到32KB的原始数据需要预处理、FIR滤波和归一化。断点检测,所有处理后的数据仍然存入后续的SRAM地址中。检测出的孤立词分别存入独立首地址后面。

1.4语音采集实时采样

锁相环PLL给予WM8731工作在18.4MHz时钟频率下,通过I2C总线控制器设置WM8731工作在8kHz的采样频率下。图5为在嵌入式逻辑分析仪(SignalTapⅡLogicAnalyzer)下语音采集控制器的采样图。

图5为实时采集图,测试人现场读入语音数据,模块实时进行语音采集回放。从图中可见,左对齐语音采集过程一共有19个脉冲,其中前16个脉冲为有效语音数据提取脉冲,后3个脉冲为将来处理扩展预留。有效语音提取出来之后便存人SRAM中。该模块通过计数器,从启动录音开始,自动录制4s的语音信号。

2语音录制回放仿真

经WM8731采集的语音信号转换并存储于SRAM,然后用SRAM中的数据将SRAM的语音数据导出,图6为语音采集模块处理后作者录入的数字符号“1234”效果图。

图6是通过DE2控制面板软件读取SRAM前256KB数据(地址:O~0x1FFFF)在Matlab软件上画出来的图形,同时为了对比,通过Matlab自带的[y,fs,bits]=wavread(‘Blip’,[N1N2]),进行同样话语的录制,用sound(x,fs,bits)对声音进行回放,仿真结果见图6、图7。从仿真图可看出,以Matlab平台为标准,FPGA实时采集与现实吻合。

3结语

该系统充分利用了FPGA的高速处理能力,自行设计采集模块和I2C协议驱动模块,并通过AWALON总线挂载在Nios软核上,很好地实现了实时高速采集回放,充分体现了FPGA的优越性能。同时结合SoPC设计理念,使系统一片式整合。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多