System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可是设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以再ISE中进行调用。或者直接生成比特流下载文件。能够加快DSP系统的开发进度。

用System Generator进行仿真

1、必须包含的模块:Gateway In、Gateway Out、System Generator、以及Xilinx定点运算单元。

2、对于系统设计中有精确时钟限制的外部接口模块,使用System Generator设计不是最佳方法,此时可以利用HDL等方法实现,然后通过System Generator工具提供的Black Box导入Sysgen工程中即可。

System Generator Blockset

1、主要包括:Xilinx Blockset、Xilinx Preference Blockset 和 Xilinx XtremDSP Kit三个库函数块。

2、Xilinx Blockset包含了所有在Simulink中构建数字信号处理系统和其他FPGA数字系统的模块。

3、Xilinx Preference Blockset 是更高层次的模块,都是由Xilinx Blockset中的模块组成的,降低了开发难度,并且具有较高的可靠性。

信号数据类型

1、Xilinx Block的输出格式可以设定为:Full precision和User-defined precision

Full precision:会在运算中自动进行位宽扩展

User-defined precision:对输出结果进行截位(wrap)或饱和(saturate)处理(用户设置)。

2、在System Generator中,点击Format –> Port/Signal Displays –> Port Data Type 即可显示每个模块输入输出的数据类型。

3、当Simulink无法确定数据类型和采样速率时,会报错,通常这种情况出现在有反馈的情况下。这时可以通过添加一个Assert模块对信号进行强制制定或重新定义。且不占用硬件资源。

4、Gateway In可以设定Sample Period,值越大,采样点越少。一般来说,对于同一组Gateway In,sample period应该是一样的,即采样率时一样的。所以当修改一个Gateway In的Sample Period时,记得同时更新同一级的Gateway In的Sample Period。

5、采样率变换,利用模块:Up sample和Down sample。System Generator中不同颜色代表不同的采样率。可以点击Format –> Sample TIme Colors

利用Matlab产生测试向量

1、使用From Workspace block产生测试向量。注意数据必须是2xn矩阵:

colume 1 = TIme values

colume 2 = data values

例如:[1:101; sin(2*pi*[0:.01:1])]

2、使用To workspace block将sysgen数据输出到MATLAB进行分析

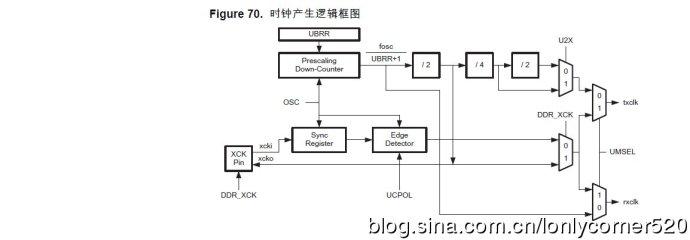

时钟周期

1、Simulink system period为Simulink仿真时钟周期,该周期必须是设计中所有采样周期的最大公因子,比如系统中有3个采样周期(2、3、4),那么Simulink system period为1。

2、如果FPGA系统时钟周期是10ns,那么Simulink系统周期,2s、3s、4s三个采样周期分别对应FPGA器件实现时的10ns、20ns、30ns、40ns。另一种做法是将Simulink系统周期就定义成FPGA的系统周期,这样省去了时钟周期间的换算。

3、可以用Clock Enable Probe模块来实现潜在的时钟使能信号。

APP下载

APP下载 登录

登录

热门文章

热门文章