1系统架构

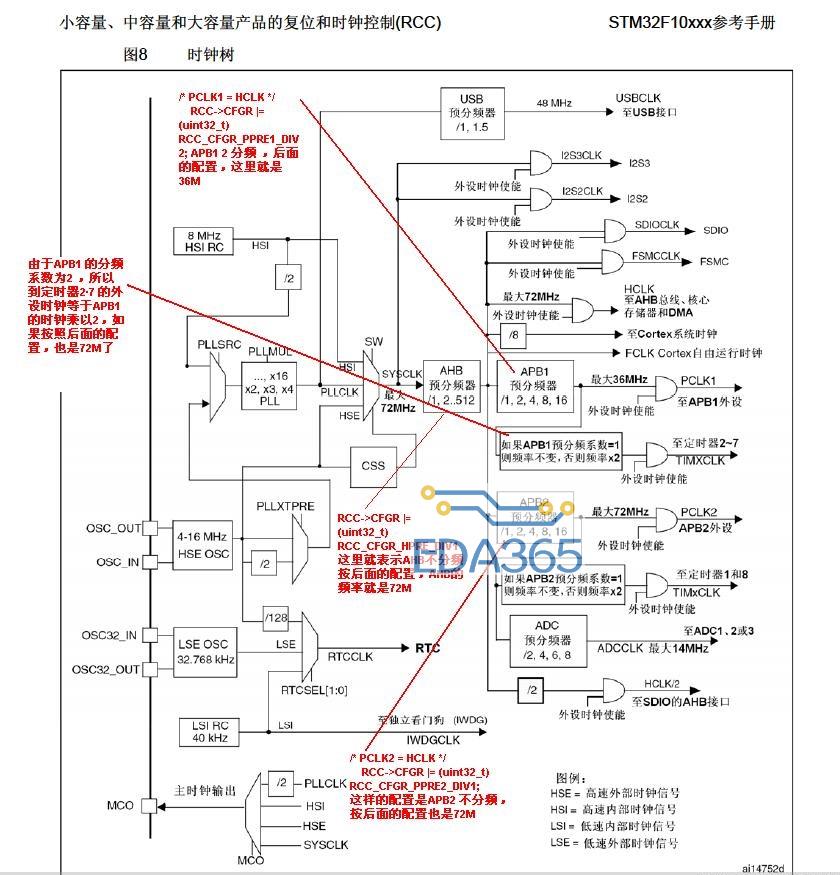

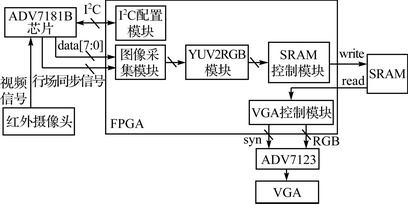

红外视频监测系统的FPGA部分由5个模块组成,分别是I2C配置模块、图像采集模块、YUV2RGB模块、SRAM控制模块、VGA控制模块。配置模块通过I2C总线来对ADV7181B芯片进行配置。配置成功后,ADV7181B将产生图像采集模块所需的行场同步信号,并将红外摄像头输入的复合视频信号转化为标准的NTSC/PAL制式,输入到图像采集模块;图像采集模块用来提取YUV(BT656)图像中的有效数据;YUV2RGB模块将YUV图像数据转化为RGB格式以供VGA显示;VGA控制模块用来产生D/A芯片(ADV7123)工作的同步信号、图像数据,以及控制图像数据从SRAM中读出。红外视频监测系统框图如图1所示。

2系统硬件设计

2.1I2C配置模块

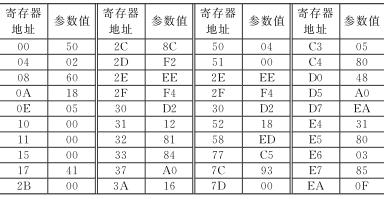

ADV7181B是Analog公司的一款应用广泛的视频解码芯片。该芯片自动监测输入的复合视频信号,通过I2C总线配置接口,可选择图像输出方式(NTSC/PAL等),本文以输出NTSC制式视频图像为例,给出了所需配置的寄存器地址和配置参数值,NTSC制式视频图像寄存器地址和配置参数值如表1所列。

图1红外视频监测系统结构框图

表1NTSC制式视频图像寄存器地址和配置参数值(十六进制)

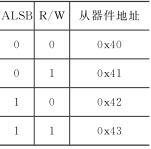

表2从器件读写地址

ADV7181B芯片作为I2C总线通信的从器件,其ALSB引脚电平的高低所对应的器件地址是不同的,从器件读写地址如表2所列,本系统将ALSB引脚接地,写地址设置为0x40,所有地址代码用十六进制表示。

2.2图像采集模块

NTSC默认输出的图像为奇偶场交替输出,数据信号和行场同步信号时序关系如图2所示。奇偶场分别有253有效行,本文获取其偶数场图像用于传输和显示。BT.656定义了一个并行的硬件接口,传输的视频图像格式为YCbCr 4:2:2(Y为亮度信号,Cb、Cr分别为蓝色信号分量和红色信号分量)。一行图像数据的有效像素为720,一个像素占用两个字节,格式为CbYCrYCbYCrY。本文采用每两个像素即每输出CbYCrY获取一组CbYCr,这一组数据通过移位寄存器得到3路8位的并行数据送入YUV2RGB模块,此时有效像素被压缩成360个。720×525的图像数据通过本模块的采集,可传送的有效像素为360×253。

图2数据信号和行场同步信号时序关系

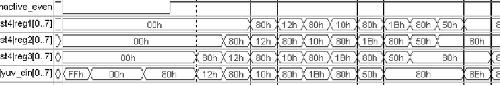

图3图像数据采集时序

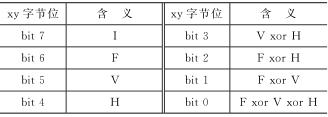

一行图像数据的起始/结束(SAV/EAV)和所在数据帧的位置是根据BT656图像格式(即根据检测到的ADV7181B输出数据序列“FF,00,00,xy”)来判断的。奇数场的有效行起始时xy为0xC7,结束时xy为0xDA;偶数场的有效行起始时xy为0x80,结束时xy为0x9D。xy各位含义如表3所列。最高位bit7为固定数据1,F=0表示偶数场,F=1表示奇数场;V=0表示该行为有效视频数据,V=1表示该行无有效视频数据;H=0表示为SAV信号(行起始),H=1表示为EAV信号(行结束);低4位为保护信号。

表3xy字节各位含义

图3为SignaltapII观测到的图像数据采集时序。hactive_even高电平期间为有效图像数据采集阶段,yuv_din为从ADV7181B输出的8位并行图像数据,当“FF 00 00 80”到来时,开始采集偶数场图像的一行有效像素,其中黑线分隔的reg1、reg2、reg3为提取的3路即将送入RGB转化模块的图像数据。

2.3YUV2RGB转化模块

VGA显示器所需的图像数据为RGB格式,所以需要对YCrCb进行转化,转化公式如下:

R=1.164(Y-16)+1.596(Cr-128)(1)

G=1.164(Y-16)-0.813(Cr-128)

-0.392(Cb-128)(2)

B=1.164(Y-16)+2.017(Cb-128)(3)

浮点运算需要大量的FPGA资源,进而影响系统性能,本系统采用查找表来简少FPGA运算量,将上式中5个不同的系数分量分别编写查找表。为进一步简化运算将(1)式两边乘以2,以式(1)为例,查找表如下:

always @ (in)

case(in)

ue10cd0:out = 10ue10cd0;

ue10cd1:out = 10ue10cd3;

ue10cd2:out = 10ue10cd6;

ue10cd3:out = 10ue10cd10;

ue10cd4:out = 10ue10cd13;

ue10cd5:out = 10ue10cd16;

……

设a=2×1.164Y,b=2×1.596Cr式(1)简化为:2R=a+b-446。若(a+b)>446,则R分量值为(a+b-446)/2;若(a+b)446,则R分量值为0。

同理可算出G、B分量,即完成了YCrCb到RGB的转化。由于SRAM数据线为16位,各取3路8位RGB分量的R信号(5位),G信号(6位),B信号(5位)写入SRAM。当RGB_wrdata为非零图像数据时,将其写入SRAM即实现了分辨率由720×525向360×250的转化。

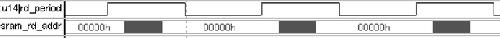

2.4SRAM读写控制模块

当写入360×250的视频流数据量所需的存储空间为100 KB时,由于FPGA内部存储资源有限,本系统通过外部SRAM来存储图像数据。SRAM所使用的型号为IS61LV25616,存储空间为256K×16位,满足图像存储需求。SRAM芯片工作不需要刷新,读写时序也不复杂,当向SRAM写入数据时先建立地址和数据,然后使能写信号wr_n,在wr_n保持一定时间后将其复位,最后释放地址总线和数据总线;当从SRAM中读出数据时,置wr_n为高电平,同时使能SRAM读出信号,并建立地址。一帧图像的偶场信号写入SRAM的波形如图4所示。

图4一帧图像的偶场信号写入SRAM的波形

2.5VGA控制模块

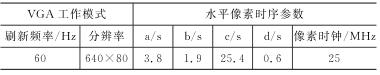

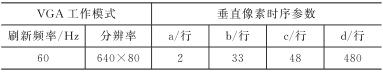

ADV7123是一个3路10位信号输入的高速D/A芯片,采样速度最高可达330 MHz,可用于多种显示系统。本文采用标准的VGA显示模式640×480@60 Hz,VGA水平/垂直时序参数如表4、表5所列。

表4VGA水平时序参数

表5VGA垂直时序参数

VGA控制模块产生ADV7123的工作时序,当一帧图像的偶数场写入SRAM时,奇数场时间段则不再向SRAM中写数据,而是从SRAM中读出图像数据,这样即可实时传输图像。为了实现图像的完整性,640×480可显示区域为360×250,具体代码如下:

if(odd_period)//奇数场

begin

if(V_Cont>=Y_START V_ContY_START+250)//Y_START为图像场消隐区

begin

if(H_Cont>=X_START H_ContX_START+360 )//X_START为图像行消隐区

sram_rd_addr=sram_rd_addr+18ue10cb1;//SRAM数据读出地址

else

sram_rd_addr=sram_rd_addr;

end

在VGA的有效显示区域内,将SRAM读使能,地址自增,即可将图像信号从SRAM中读出。读出的16位数据中,高5位为R信号分量,中间6位为G信号分量,低5位为B信号分量;将这3个分量赋给各自颜色分量的最高位,低位补零即得到VGA工作的RGB信号输出。图5为奇数场SRAM读出地址时序。VGA控制模块从SRAM中将图像波形读出,rd_period为高电平时读出一帧图像的偶数场,sram_rd_addr范围为0~360×250。

图5奇数场SRAM读出地址时序

3硬件设计及实验结果

3.1硬件设计

FPGA芯片采用Altera公司Cyclone II系列的EP2C35F484C6,它具有较高的性价比,内部有33 216个逻辑单元,322个外部引脚、4个PLL、66个M4K RAM块、8个I/O BANK。工作需要1.2 V电压和3.3 V的I/O电平。本系统采用的芯片封装为FBGA,PCB制板采用的是4层电路板。由于板子上使用了A/D、D/A数模混合信号的芯片,要使电路板达到好的性能,就需要严格的遵守PCB布板规则:

① 模拟复合视频信号输入到ADV7181B的走线要尽可能短,数据线和时钟线也要尽可能短。

② 在电源引脚附近添加去耦电容,滤波电容。

③ 对芯片的每个电源(AVDD、DVDD、DVDDIO、PVDD)分开供电。

④ 分隔数字部分和模拟部分,数字地和模拟地通过单点连接。

3.2实验结果

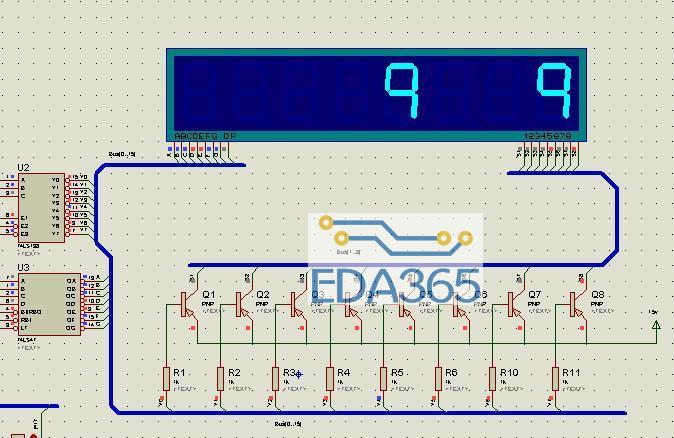

将设计调试好的PCB电路板,接上电源、NTSC制式红外摄像头和VGA显示器进行联调,红外图像实时显示良好,实验结果如图6所示。调试结果证明了该图像采集系统设计的正确性。

结语

实验结果表明,该红外实时采集系统工作稳定。该系统基于FPGA技术,结构简单,可以灵活地根据需求配置系统,具有开发周期短、扩展性好、成本低的特点,有较高的应用价值。

图6实验结果

APP下载

APP下载 登录

登录

热门文章

热门文章