本文所要提及的逆变电源的特殊性在于他不但能够提供三相正弦平衡电源,而且要保证在任何内外界环境干扰条件下,任何两相间的相电压幅值与频率保持高度稳定(进行工作状态)。因此采用的逆变主电路是由3个单相全桥式逆变器组合成的三相逆变电路如图1所示。

如何控制逆变主电路中开关器件的工作成为本系统能够达到要求的关键,为了加快开发进度,更为重要的是提高设计的灵活性和精确度,引入现代EDA(电子设计自动化)技术,采用VHDL硬件描述语言进行控制逻辑编程,配置于大规模可编程器件CPLD/FPGA 芯片上,对主电路的工作状态进行控制,以获得符合要求的电源电压及波形。

CPLD/FPGA可以在办公室或实验室里方便地设计出所需的专用集成电路,具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改,极大地提高了电子系统设计的灵活性和通用性。

2 调制方案

脉宽调制(PWM)是指工作频率不变(即工作周期不变),通过改变开关器件的导通时间或截止时间来改变占空比,控制输出的电压脉宽,通过控制脉宽系列的变化规律来满足输出的要求。

为满足设计要求,本文采用正弦波脉宽调制(SPWM)方法,当然SPWM波形产生的方法也是多种多样,有自然采样法、规则采样法和直接面积等效法等。与其他方法相比,等效面积SPWM算法具有算法简易、谐波含量小、输出波形贴近理想值等特点,因此采用等效面积SPWM算法进行脉宽调制,进而实现对主电路器件的运转周期过程进行控制。

2.1 建立数学模型

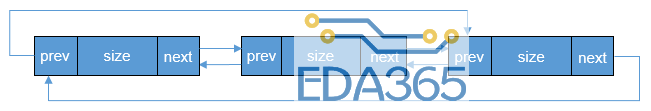

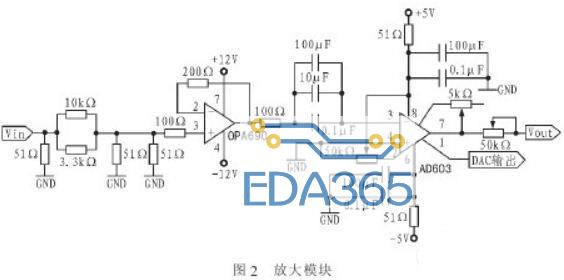

首先把单个周期正弦波形分为N等份,然后如图2所示将每一等份的正弦弧线与横轴所包围的面积用与其面积等同的等高不等宽的矩形脉宽来代替,矩形脉宽的中点与正弦弧线在横轴上的投影中点要重合。于是,由N个等高的矩形脉宽系列构成的波形就等同于正弦波形[1],这一系列矩形脉宽的宽度及其开关(即开关器件的导通截止时间)可用数学方法进行计算。

如图2所示是第K个脉宽,对应的正弦弧线与横轴所包围的面积SAK,脉宽矩形面积SRK。

其中,M为调制参数。

由于将正弦波形分为N个等份,每一等份的弧度为

第k个脉宽的宽度为:θpk=a3k-a2k,前后两低电位的宽度为:

2.2 设计计算

N取12,根据正弦波形的对称性,实际矩形脉宽宽度只要算出3个就足够了,取正半周的前半部分进行计算,利用数学工具Matlab易算出如表1所列的结果(其中M取0.813,θmk为第K个等份的中点,表1中所列出的主要是对下文叙述有用的数据)。

3软硬件的实现

由于采用CPLD/FPGA作为控制电路的硬件载体,通过VHDL硬件描述语言的编程对硬件进行功能的描绘,运用的是数字化的控制方式,因此必须将表中的数据进行转换。假设每个等份的计数值为600,将表中的数据皆与(600/0.523 598 77)相乘并取整以便VHDL编程。

笔者接入的晶振为100 MHz,根据相电压的频率X,首先对他进行(100×10 6/X)分频,因此第一步设汁一个数控分频器作为主频,不但可以达到要求,还便于实验的调节。

每个脉宽产生的设计思路是,设计一个可逆计数器,顺序是299-0-0-299,取出相应的脉宽一半的数值(转换后),将数值与计数器的变量进行比较,若变量大则输出0,否则输出1,这样保证了脉宽准确地处于等份的中央。

由于电压波形的每个周期内要求有12个脉宽,且每个脉宽的宽度有严格的变化规律,因此,在设计中,每个周期对应的计数量为600×12。设计一个0~599计数器CNT1,每计到599时,产生一个脉冲进行再计数CNT2计数范围为0~11,这样在CNT从0~11变化一趟对应波形的一个周期。所以结合CNT1和CNT2可以按规律取出对应的脉宽序号,通过查寻方式取出对应的脉宽宽度一半的数值,用于比较产生脉宽,同时加入正负半波的标志位FIAGA,便于对单相全桥式逆变器各开关器件的控制。

以上叙述的是对单一相电压波形的调制设计,还有另两相A,B,为满足相位平衡,可直接在计数器CNT1中加入另两相的脉宽比较输出,但是取出用于比较的脉宽序号是不一样的,B相滞后A相 C相又滞后B相 因此B相在CNT2为4时的脉宽序号与A相在CNT为0时的脉宽序号一致,C相同理,同时还要加入各自的正负半波的标志位FLAGB,FLAGC。

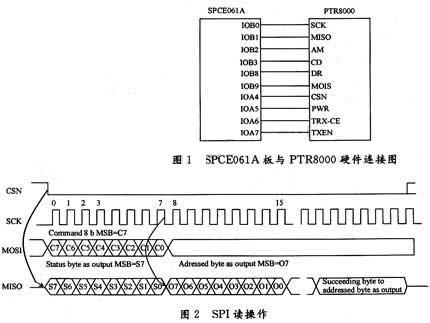

其实逆变电源的特殊要求就在于在三相负载不平衡条件下能够保证输出的电源品质不变,因此,每个相的脉宽必须各自能够进行自我调节,以达到各相电压幅值一样,在编程中,必须对每相的电压调节分开,这样,相同脉宽序号下,各相的脉宽宽度并不一定相同,还要根据反馈进行调节,脉宽相应的数值是变化,因此,对每一相的脉宽宽度分开利用查寻表(如图3所示,有3个表储器A,B,C)的方式进行获取。

以下是利用VHDL编写控制程序的部分内容:

利用EDA设计工具软件Max+PlusⅡ进行波形仿真,仿真结果如图4所示。

从仿真结果可以清楚地看到,波形每个周期时间为2.5 ms(相当频率400 Hz),对于A相,在FLAGA和A的与与非组合下,为对角管子T1T2提供信号A12,为另一对对角管子T3T4提供信号A34,而且保证了同一桥臂的上下两管子不会同时导通,所以在设计当中,不用设置死区时间,降低系统设计的复杂度,从而提高了系统的可靠性,其余两相同理,再利用Gw48-GK实验开发系统板[3],通过下载到Altera公司的EP1K30TC144-3芯片上进行硬件测试,结果完全符合要求。

4 结 语

利用CPLD/FPGA作为硬件电路,采用VHDL等硬件描述语言对硬件的功能进行编程,加快了系统的研发进程,采用数字化的控制方式,大幅度提高了逻辑控制的精确度,实时控制效果好,实践证明CPLD/FPGA芯片可以代替传统的复杂的电路,而且可以大比例地缩小电路的硬件规模,提高了集成度,降低开发成本,提高系统的可靠性,为电源逆变控制电路的设计开辟了新的天地。

APP下载

APP下载 登录

登录

热门文章

热门文章