作为SoC开发计划的一部分,软件的重要性日益提高,这一点没有放过。经过深思熟虑,软件现在消耗了分配给SoC项目的大约70%的资源。而且,如果软件无法正常运行,SoC也将无法正常运行。

因此,找到EDA公司通过基于FPGA的原型系统解决该问题也就不足为奇了。Synopsys说,他们已经交付了10多年,在此期间,该产品已经发展了六代。

它提供的产品是HAPS(高性能ASIC原型系统的缩写)系列,旨在帮助团队更快地将其产品推向市场,并且重要的是,避免了昂贵的转售。

但是Synopsys在该领域并不孤单。竞争对手的EDA供应商Cadence Design Systems刚刚推出了Protium系统,并认为这代表了“最先进的技术”。

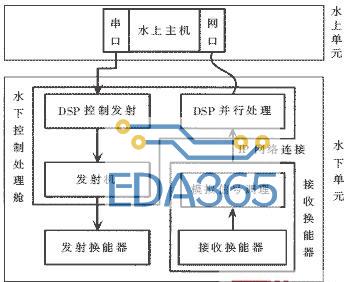

Protium构成了Cadence系统开发套件(SDS)的一部分,该系统套件由四个平台组成,旨在加速集成,验证和启动设计(见图2)。根据Cadence的说法,设计团队可以使用Suite将系统集成时间缩短两倍。

Cadence系统和验证小组产品管理和市场营销总监Frank Schirrmeister表示:“ Protium是系统开发套件开发的又一步,该套件具有一组处理仿真,仿真和FPGA原型的引擎。自2011年以来,每年都有更新。现在,我们正在添加基于FPGA的快速原型开发平台。”

但这不是Cadence在该领域的首个产品。“我们以前有一个称为RPP的系统,” Schirrmeister指出。“那是基于Altera FPGA。”

实际上,Schirrmeister指出了可应对一般验证挑战的产品组合。他说:“我们有钯和Pro。” “两者共享相同的软件前端,但是区别在于它们各自的容量,硬件调试和速度。” 钯金是更大的产品,能够处理多达20亿个ASIC门的设计,但更类似于仿真引擎。两者中较快的Protium支持性能优化。

高级产品营销经理Juergen Jaeger解释了Protium的好处。“它提供了自动处理最复杂的时钟方案和无限数量的设计时钟的能力。通常,快速原型系统在这方面有严格的限制。Protium还可以更有效地处理内存上载和下载;这对于软件开发目的。最后,它支持“按构造”消除FPGA保持时间违规。”

但是Protium的门设计限制为100m,而HAPS可以处理多达144m的门设计。为什么会有这种差异?

Schirrmeister解释说:“处理器子系统的平均设计尺寸约为75m ASIC门,因此停止使用100m门是正确的地方。较大的设计需要在仿真器上进行处理。”

Jaeger指出了与系统相关的原因。“ HAPS系统上的144m门是由用户必须将三个HAPS板连接在一起,然后必须在这些板之间手动划分设计来实现的。Protium可以自动完成。Protium用户可以将多个系统连接在一起以生成一个如果他们愿意的话,可以使用更大容量的系统。”

Protium和HAPS确实具有一个共同的元素:Xilinx FPGA的使用。两种系统都使用V7-2000T,每个系统都可以处理约12.5m的闸门。

入门级Protium配置具有两个FPGA,可处理多达25m个门的设计。但是,Protium可以容纳多达8个FPGA,提供100m的门容量。

有两个基板选项,带有两个和四个FPGA,Protium每个机箱可容纳两个板。据说使用Protium可以使设计速度提高四倍。它的容量是RPP系统的四倍,而内存则是三倍。Cadence表示,总体而言,采用钯设计流程时,编译时间可提高五倍。

Schirrmeister表示:“ Protium与市场上其他系统之间的主要区别在于,我们提供了硬件和软件平台。我们已经将前端从Palladium系统中移植到了FPGA上。这意味着Protium具有自动化流程,可以帮助大大加快设计的启动和运行;我们说是几周而不是几个月。

“但是,如果用户希望手动优化设计以提高速度和容量,Protium可以做到这一点。”

Protium流程包含三个步骤。首先是导入,编译和综合设计。然后,必须将设计划分为多个FPGA。此时,Protium可以将门时钟和锁存器转换为FPGA友好结构。这将为每个FPGA生成一个单独的网表用于后续布局和布线,以及一个用于验证设计功能的验证模型。最后,FPGA放置和布线为FPGA生成单独的位文件。

Protium的性能也是可调的。在其全自动配置下,Protium的工作频率范围为3至10MHz。但是,选择手动指导后,系统可以以最高30MHz的速度运行。另一个选择是席尔迈斯特所说的“黑拳”。在这种配置中,具有直接的时钟映射和直接连接的大容量存储器,可将系统性能提高到100MHz。

Protium是基于周期的,在称为FCLK的概念时钟的每个周期更新一次设计中的每个网络。这是由编译器自动生成的,编译器还确定了频率。Cadence还声称可以与时钟树转换竞争,并说这消除了FPGA和板时钟的限制。通过消除这些限制,它增加了FPGA的布局和布线速度,并获得了更好的质量结果。

据Cadence称,基于FPGA的原型设计继续吸引着更多的用户。大多数使用仿真的人员还利用了基于FPGA的原型设计,而80%的数字ASIC均使用基于FPGA的系统进行了原型设计。Schirrmeister断言:“超过一半的原型用户将增加时间作为他们的主要挑战。”

Schirrmeister认为,这是Protium的亮点之一。他承认:“这一领域具有挑战性,涉及的问题包括内存建模和分区。团队可能需要花费几周的时间来获取RTL并将其放入FPGA系统中;他们需要更改RTL模型和存储器。为此,团队需要验证结果是否符合预期。

“有了Palladium前端的流程,内存创建,时钟处理和分区都将自动处理。”

在该过程中的某个时刻,也可以选择使用钯。他继续说:“如果您发现错误是由于更改了RTL而引起的,那么您可能会发现基于FPGA的方法功能有限;它不如仿真或仿真好。因此,用户可以使用网表并在Palladium中启用它。更快速。”

Protium是否会获得更多容量?Schirrmeister总结道:“基于FPGA的原型设计和仿真之间的最佳结合点将来可能会改变。”

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多