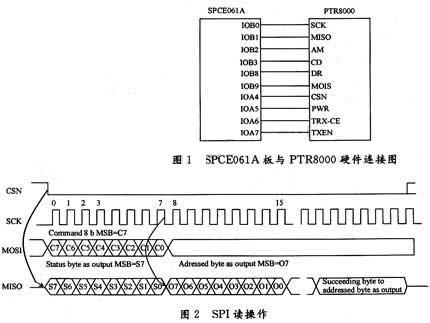

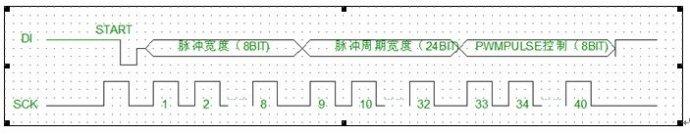

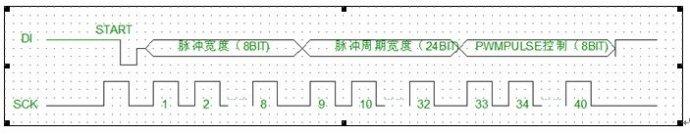

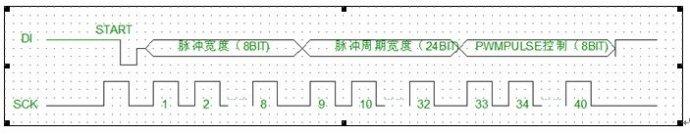

1.线路状态:在平时不发送数据的时候,DI 为高电平。SCK为低电平。2.起始位:SCK 为高的时候,DI 的下降沿决定了一次数据传送的开始。也就是说,在发送数据的时候,SCK为高电平的期间,DI 不允许变化。

3.起始位有效后,SCK的上升沿输出数据。

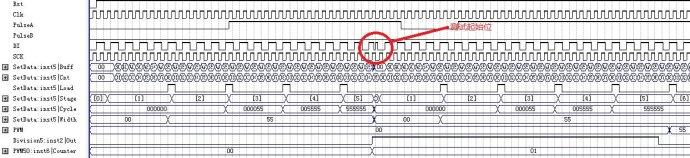

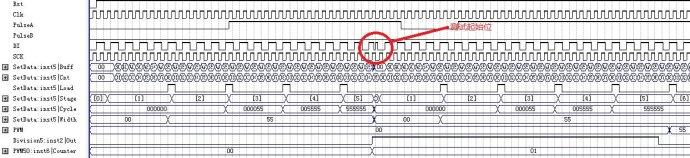

4.时序图

5.所有数据低位在前

数据为单向发送,目的是产生宽度可频率可以调节的信号。同时产生一路Pwm信号,本设计只是发送数据部分

代码:

module SetData(Rst,SCK,DI,Width,Cycle,PWM);

input SCK,DI,Rst;

output reg [7:0]Width;//脉冲宽度

output reg [23:0]Cycle;//周期

output reg [7:0] PWM;//Pwm数据

reg [7:0]Buff;

reg [7:0] Buff1;

reg [2:0]Stage;//状态变量

reg [5:0]Cnt;

reg Load;

reg INIT;//起始位标记

parameterStatus0= 3b000;//状态定义

parameterStatus1= 3b001;

parameterStatus2= 3b010;

parameterStatus3= 3b011;

parameterStatus4= 3b100;

parameterStatus5= 3b101;

parameterStatus6= 3b110;

parameterStatus7= 3b111;

always @(negedge Rst,negedge SCK)//产生串并转换完成信号(8bit)

begin

if(!Rst) Load<=0;

else if ((!SCK)&&(Cnt==8))

Load<=1;

else Load<=0;

end

always @(negedge DI)//检测起始位

begin

if(SCK==1)INIT<=0;//标记到init 中

else INIT<=1;

end

always @(negedge Rst,posedge SCK,negedge INIT)//状态转换

begin

if ((Rst==0) || (INIT==0))//强制到状态0

begin

Stage<=Status0;

Buff<=0;

end

else if ((SCK==1)&&(Stage==Status0)) begin Stage<=Status1;Cnt<=0; end

else if ((SCK==1)&&(Stage!=Status0))

begin

Buff<={DI,Buff[7:1]};

Cnt <= Cnt+1;

if (Cnt==8)

begin

Cnt<=1;

Stage<=Stage+1;

if (Stage==Status7) Stage<=Status0;

end

end

end

always @(posedge Load,negedge INIT)//组合出需要的数据

begin

if (INIT==0)//如果是起始位,所有数据清零

begin Width <=0;Cycle<=0; PWM<=0; end

else

//begin

case(Stage)//不同状态下的数据输出

//Status0:

Status1: Width<=Buff;//脉宽数据

Status2: Cycle<={ Cycle[23:8],Buff};//周期数据

Status3: Cycle<={ Cycle[23:16],Buff,Cycle[7:0]};

Status4: Cycle<={ Buff,Cycle[15:8],Cycle[7:0]};

Status5: PWM<=Buff;//PWM数据

endcase

// end

end

endmodule

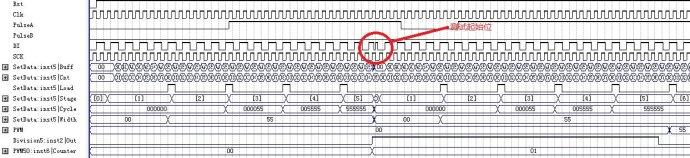

仿真结果

注意图中认为中断了数据发送(通过设置起始位来实现)。

初学verilog语言,用的可能不够规范,主要是不习惯不能在不同进程里对同一个变量赋值的约束,只好加一个init变量进行信号传递。

热门文章

更多

热门文章

更多