1 PCI Express总线简介

Intel在2001年首先提出了替代PCI总线的新总线技术——PCI Express,当时Intel称之为“3GIO”,意为“第三代l/o标准”。PCI—SIG于2001年、2006年先后提出了PCI Express 1.o/2.0规范。

PCI—Express总线具有点对点串行互联;双通道、高带宽、传输速度快;灵活的扩展性;低电源消耗,电源管理功能;支持设备热拨插和热交换;使用小型连接,节约空间,减少串拢;在软件层保持与PCI兼容等特点。

2 PCI Express总线系统结构

PCI Express的基本结构包括根组件(Root Com—plex)、交换器(Switch)、桥(Bridge)和终端设备(End—point)。集成在北桥芯片中的根组件,用于CPU和内存子系统于I/O设备之间的连接。交换器支持在不同终端设备间进行对等通信。桥是指PCI Express到PCI或PCI—X的桥接设备,实现PCI Express—to—PCI和PCI Express—to—PCI—X桥接功能,用来支持传统PCI/PCI—X设备。

终端设备可以包括多个功能模块,可以通过其有且仅有的一个上游端El与根设备或Switch连接。通常,终端设备指的是系统的外围设备,如以太网、USB或图形设备。如图1所示。

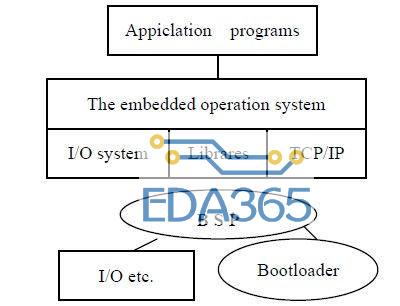

PCI Express体系结构采用分层设计,从下而上分别是:物理层(Physical Layer)、数据链路层(Data Link Layer)和事务层(Transaction Layer)。如图2所示。

3 PCI Express接口板的硬件设计

PCI Express总线接口的实现大体有2类方法:一类是使用FPGA/CPLD等可编程器件开发逻辑转换电路。根据实现功能的多少,所需的等效门密度约为5 000~15 000门,可自行编程或是购买已有IP核的产品实现;另一类是使用专用的接口芯片。前者开发成本高、难度大、周期长、测试设备昂贵,但是批量生产成本低,适合大规模全定制或半定制ASIC:的生产。而后者实现了PCI Express总线的物理层、数据链路层和事务层的控制逻辑,用户可以专注在其应用方面的开发,而不必再调试PCI ExpipeSS接口,开发难度大大降低,是实现.PCI Express接口的有效方法。

该设计选用PLX公司的专用接口芯片PEX8311作为桥接芯片来实现PCI Express接口设计。

3.1 PEX8311芯片简介

PEX8311是PLX公司开发的第一款PCI Express总线到本地总线的接口芯片。它符合PCI Expressl.0a基本规范,并且其本地端寄存器与PLX公司的PCI系列接口芯片基本兼容。

3.1.1 PEX8311的特点

(1)集成了单通道、全双工2.5 Gb/s传输的PCI Exptress端口;

(2)本地总线配置支持8位、16位和32位的总线结构;

(3)支持复合和非复合的操作模式;

(4)高性能DMA数据传输支持块模式,集散模式,循环队列管理和命令模式;

(5)支持端点和根组件模式;

(6)芯片小型封装,适合紧凑的电路板设计;

(7)芯片低功耗设计;

(8)3.3 V的I/O并且兼容5 V系统;

(9)串行E。PROM用来可选择的导入配置,支持接口和Micr’OWire接口;

(10)有8 KB的通配共享RAM。

3.1.2 PEX8311的内部结构

PEX8311作为一种桥接芯片,在PCI Express总线和本地总线之间传递信息。它可以作为主控设备去控制2个总线,也可以作为目标设备去响应2个总线。它通过内部的控制逻辑模块、内部总线状态机模块和本地总线状态机模块共同控制芯片的数据传输。PEX8311的结构如图3所示。

3.1.3 PEX8311的地址空问及数据传输方式

PEX8311的地址空间分为PCI Express地址空间和局部地址空间。前者包括配置寄存器、I/O空间、内存映射I/O(32位)、可预取内存空间(64位);后者包括空间0、空间1、扩展RAM空间。

PEX8311支持3种数据传输方式。分别是:主模式(Direct Master)、从模式(Direct Slave)、直接存储器存取模式(DMA)。

3.2 PCI Express接口板的硬件设计方案

采用PEX8311的接口板设计在逻辑上可分为3个功能模块:PCI Expr。ess接口部分、E2PROM部分和本地总线部分,如图4所示。

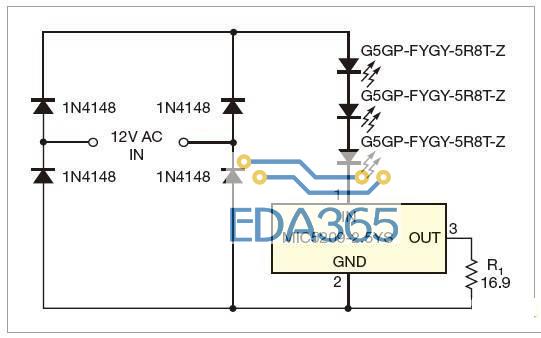

PEX8311提供完备的PCI Express从设备支持,PCI Express接口部分的信号线可以直接与PCIExpress连接器(俗称金手指)连接。其中,REFCLK±是一组差分时钟,它由系统主板提供。2个参考时钟都要求保持在正常工作频率100 MHz的±300 ppm之内。PRSNT1/PRSNT2信号线用于检查附加卡是否插入连接器。此次设计中将PRSNl和PRSNT2相连,这样当接口板插入到PCI Express连接器时就能进行存在检测。在此,使用+3.3 V和12 V电源,由于不使用3.3VAUX,将其连一个电容并接地。PCI Express接口部分电路,如图5所示。

PEX831l提供两个串行E2PROM接口,在系统上电后读取配置信息。SPI串行E2PROM是PCI Ex—press的配置E2PROM。它主要用来控制PCI Express的性能。SPI串行E2PROM可以用来预配置片上8 KB共享缓存。MicrOWire串行E2PROM是本地配置E2PROM,它用来控制本地总线行为,并分配合适的地址范围。

本地总线部分是此次设计中的重点。PEX8311与CPLD相连的部分包括LA地址总线、LAD数据总线、LBE字节使能信号、Lw/R读写信号等。

本地总线端的数据使用的是8位数据,在这种模式下LBE1和LBE0提供地址线线[1:O]。CPLD用来控制PEX8311的读写操作和数据传送。

SRAM用于存放用户的数据和代码,为程序的运行和保存临时文件提供空间。SRAM的数据/地址线与PEX8311相连,SRAM的管理由CPLI实现。XRl6C854.是一款通用的串口通信控制器。它带有128位的FIFOs和独立的接收/发送FIFO计数器,完成最基本的串行通信功能。其数据/地址由PEX8311提供,读/写/片选由CPLD控制。RS 422收发器要求传输速率高达10 Mb/s,选择MAXII公司的M_AXl3087ECPLD如何设计实现PEX8311本地总线控制对整个功能的实现起着至关重要的作用。PEX8311通过本地总线与本地设备进行通信。它支持3种本地总线数据传输方式:单周期模式、4周期突发模式、连续突发模式。下面简要介绍如何用CPLD实现单周期模式。

图6为PEX8311的单周期读写的VHDL语言时序控制状态机设计。状态O为空闲状态,如本地总线请求信号LHOLD被置为1,则转到状态1,否则停留在状态O。状态1为总线保持状态,在此状态下应将本地总线响应信号LHOLDA置为1。如ADS信号为O且LW/R为1转到状态2;如ADS信号为l且Lw/R和BLAST都为0转到状态3,这次操作为单周期读。状态2为单周期写状态,在此状态下要置READY信号为0,以表示写数据有效,在BLAST为O时转到状态3。状态3为读写完成操作状态,当LHOLD被置为O时,表明PEX831l不再请求本地总线,转到状态O,当BLAST为0且LHOLD为1时,表明PEX8311还要进行读写数据,则转到状态1继续。

3.3 PCI Express接口板的PCB设计

PCI Express接口板的PCB设计应遵循高速信号布线设计的要求。每个信号面都应有一个完整的地平面作为参考面,这样的设计使信号走线都有最佳的电流回流途径,有效地控制串扰、EMC和信号线的阻抗,保证信号质量。PCB板上差分阻抗为100 Q±10 Q,符合PCI Express规范的要求。单端阻抗为50 Q±10 Q。PCI Express接口的物理连接由2对差分线对组成,信号线的数据传输率位2.5 Gb/s。所以必须对信号的走线进行严格的控制。从PEX8311的输出信号引脚到PCI Express接口的金手指的走线长度不能超过25.4 mm。差分线对内的2条信号线最好严格等长,公差不能超过土0.127 mm,走线途径基本相同。SRAM的频率较高,所以要注意布线的长度和路径,以保证信号的完整性。实验证明这样的PCB设计充分满足PCIExpr。ess接口信号的传输要求。

4 PCI Express接口板驱动程序及软件开发

PCI Express总线与PCI总线在软件层是完全兼容的,因此PCI Explress接口板驱动程序的开发过程与.PCI设备驱动程序的开发过程是相同的。

在Windows操作系统下,微软公司提供了DDK开发工具,同时其他公司也提供了开发工具,如VtoolsD,Driverworks,WinDriver等。用DDK进行开发,需要了解操作系统内核知识,开发难度大,周期比较长。用其他公司的开发软件,不用了解DDK的核心知识,开发驱动相对要快。其中JUNGO公司的WinDriver开发工具,在用户级(ring 3)进行核心驱动开发,时间短,并且产生的驱动程序稳定高效,支持不同的操作系统,可移植性强。用户接口函数可采用Microsoft Visual C++6.0进行开发,提供标准的动态库函数,可供VB,Vc,Delphi等工具开发的应用程序调用。用户通过用户接口函数对板卡上的资源进行调度和访问。该设计采用驱动程序开发工具WinDriver,进行相应模块的驱动程序开发,实现在 Win—dows操作系统下的安装和配置。

5 结 语

经测试,该接口板在单字读写模式下,执行程序死循环,CPU占用率80%以上,数据传送速率6 Mb/s;在突发读写模式下,执行内存块复制,CPU占用率80%以上,数据传送速率60 Mb/s;在DMA突发读写模式下,执行直接存储,CPU占用率10%,数据传送速率240 Mb/s。通过与普通PCI19054接口板的对比,PCIE。xpreSS接口板具有明显优势。这里介绍了PCI Ex-press接口板的软硬件设计。提供了PCI Express接口板设计模板,为日后军用CPCI总线功能模板向PCI-ExpreSS总线的过渡提供设计参考

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多