PCI Express是一个计算机系统总线的名称,不过大家听得最多的还是“接口”这个词。PCI Express的确是下一代的总线接口,而采用此类接口的产品,多为显卡,而PCI-E接口的显卡,也已在2004年正式面世。早在2001年的春季“英特尔开发者论坛”(IDF2001)上,英特尔公司就提出了要用新一代的技术取代PCI总线和多种芯片的内部连接,并称之为第三代I/O总线技术。随后在2001年底,包括Intel、AMD、DELL、IBM在内的20多家业界主导公司开始起草新技术的规范,并在2002年完成,对其正式命名为PCI Express。看来,新技术也并不是一促而僦的,它也需要长期的准备,这样,才会让它一面世便拥有相当的成熟度。

特点

1、点对点连接方式

和传统的PCI总线相比,PCI Express在工作方式上有了根本的革新——采用点对点总线连接方式。我们知道传统的PCI总线是以独占带宽的方式进行工作的,任何一个时间PCI总线上只能有一个设备进行通讯,一旦PCI总线上设备增多,总线控制权争用的问题就会严重制约PCI设备性能的发挥。PCI Express总线采用了点对点的连接方式,每个设备在要求传输数据的时候各自建立自己的传输通道,对于其他设备这个通道是封闭的,各个通道互不干扰,数据传输的效率因此大为提高。

2、串行的传输方式

PCI Express的数据传输为串行方式,使用“电压差动式信号传输”,即是两条线路,以相互间的电压差作为逻辑“0”“1”的表示。每两条线路组成一个通路(Lane),每个通路的理论传送速率为2.5Gbit/s,实际中可以有两个传送通路,分为上行和下行,这样PCI Express就可以工作在双工状态下,能提供更高的传输速率和质量。

3、高速率传输

PCI Express分为x1、x2、x4、x8、x16和x32几种形式。形状上看x1最短,越往上则越长。它们是向下兼容的。PCI Express x16单通道就具有5GB/s(2.5Gb×16/8=5GB/s)带宽,不过由于采用8b/10b编码,事实上的有效带宽为4GB/s(扣除20%的植入时钟信号)。同理,替代现行PCI插槽的“PCI Express x1”单通道应该具有250MB/s的带宽,而传统PCI总线的带宽为133MB/s。PCI-Express的高带宽,能实现更高的数据吞吐能力。

注:x1表示有1条数据通道,x2表示有2条数据通道,x4表示有4条数据通道,依此类推。

4、热插拔的支持(须主板支持)

PCI Express总线数据传输距离长达3m,使得各硬件子系统完全可在空间上彼此分开,只用线缆连接。它支持热插拔功能,可对所有的接入设备进行实时监控,这样硬件厂商可设计出形状和大小都符合模块化要求的部件,用户需要扩充和升级硬件时,只需要把旧的拔掉,新的插上就可以了,不用关机。

5、良好兼容性

另外PCI Express总线还在软件级别上兼容PCI规范,不需要更新操作系统和BIOS,即可使用。未来采用PCI Express总线的主板仍可支持PCI插槽,各种PCI接口的扩展卡可以低带宽模式正常运行。这就为PCI Express的迅速普及提供了基础,不需面对等待软件的尴尬。

总体系统架构

1、PCI Express基本结构

2、PCI与PCI Express总线结构比较

图-2

3、桌面、移动和服务器系统中PCI Express总线技术的应用

图-4

[page]

PCI Express的体系结构

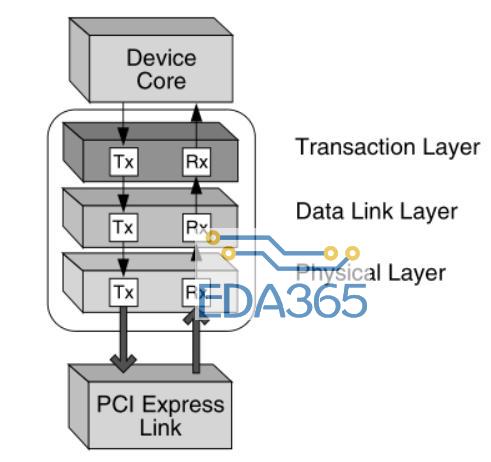

图-5

1、物理层(Physical Layer)

物理层是最低层,它负责接口或者设备之间的链接,是物理接口之间的连接,可对应于网络中OSI七层模式中的物理层来理解。

物理层决定了PCI Express总线接口的物理特性,如点对点串行连接、微差分信号驱动、热拨插、可配置带宽等。初始的单一串行PCI Express链接包含两个低电压微分驱动信号对(4线的接收和发送对)的双向连接,即“发送”和“接受”信号。数据时钟使用8/10b解码方式来达到相当高的数据速率(这一技术同时也在其它串行总线技术中,如InfiniBand和RapidIO),时钟信息直接被编码成数据流,比起分离信号时钟更好。微分信号受两个不同方向的电压驱动,初始PCI Express的链接信号发送速率为单线每个方向2.5GB/s,预计到2004年可达到5GB/s的信号传输速率,使用先进的硅技术把数据传输速率提高到10GHz(达到铜线传输的理论上最大值)。双向连接允许数据在两个方向上同时传输,类似于全双工连接,如电话系统,但是在双向传输中,各自都有自己的地线,而不像双工传输那样采用公共地线,在双向连接中可得到高速、更好质量的传输信号。单线双向信号线及传输流程如图6所示。

图6

在图中的两个红色箭头代表两个不同的方向(发送和接收)的数据包,从图中可以看出,单线数据传输每个方向只需2要芯线,即一根数据传输线,一根为地线。

PCI Express链接可以配置为x1、x2、x4、x8、x12、x16和x32信道带宽,x1带宽的链接包含4条线,x16带宽信道每个方向就有16个不同的信号对,或者64根信号芯线用于双向数据传输;终极的x32带宽信道每个方向可以提供10GB/s的数据传输速率,但是在采用8位/10位编码方式的情况下,实际速率只可达8GB/s,留有20%富余。PCI Express体系结构可以通过速度的提高和先进的编码技术来升级,但这些速度的提高、编码的改进和媒介的改变均只影响物理层,所以对于整个PCI Express架构来说升级是非常方便的。

如图7所示的是PCI Express总线数据流传输示意图。图的左边显示的是单信道情况下数据流的传输方式,因为PCI Express属于点对点串行连接,所以在单信道情况下,数据流是一个字节一个字节地传输。在图的右边显示的是多信道情况下PCI Express总线数据流的传输情况。因为有多外信道,所以数据可以依次传输到各个信道,加快了整个数据传输的速度,提高了数据传输效率,这有点类似于网络中的磁盘阵列。

在物理层的另一处重要方面就是中断。PCI Express支持两个类型的中断,现行的PCI INTx (x= A, B, C, or D) 中断被保留下来了,仍可在PCI Express总线中应用。还有一个新的中断类型,那就是MSI (Message Signaled Interrupt,信息信号中断),MSI中断可以进一步优化PCI .2/2.3设备。INTx中断方式可以用信号方式中断主机芯片请求,它可以与现行的PCI总线的驱动程序和操作系统兼容。PCI Express设备必须支持INTx和MS两种中断模式,原有设备将压缩INTx中断信息在PCI Express处理信息中。MSI中断是通过内存写处理操作边沿触发和发送的。重新编写驱动程序对于MSI边沿触发中断是非常有利的,MSI方案在使用数据包协议通过串行链接中是一种行之有效的本地中断方式。MSI在多处理器系统中任何设备都可以发送中断,比起主机直接发送中断更加有效,所以现在许多多处理器系统和I/O架构都对MSI中断技术提供支持。

2、数据链路层(Link Layer)

数据链路层的主要职责就是确保数据包可靠、正确传输。它的任务是确保数据包的完整性,并在数据包中添加序列号和发送冗余校验码到处理层。大多数数据包是由处理层发起的,基于信任,数据流控制协议确保数据包只在终端缓存空闲时传输。排队了所有数据的重试,使得信道带宽浪费现象得到有效地约束。但数据链路层在信号中断时自动重新传输数据包。传输过程如图8所示。

处理层的作用主要是接受从软件层送来的读、写请求,并且建立一个请求包传输到链接层。所有请求都是分离执行,有些请示包将需要一个响应包。处理层同时接受从链路层传来的响应包,并与原始的软件请求关联。处理层还整合或者拆分处理级数据包来发送请求,如数据读、写请求,并且操纵链接配置和信号控制。以确保端到端连接通信正确,没有无效数据通过整个组织(包括源设备和目标设备,甚至包括可能通过的多个桥接器和交换器)。

在PCI Express总线技术中,数据包类型主要有两种,那就是由处理层发起的“处理层数据包”(Transaction Layer Packet,TLP)和“数据链路层数据包”(Data Link Layer Packet,DLLP)。每个数据包都有一个可以使响应包定向于正确发起者的唯一标识符,包的格式支持32位内存地址和扩展64位内存地址。包同时还有如“非窥探”、“无严格排序”和“优先权”等属性,这些属性将应用于优化路由I/O子系统的数据包。

处理层包括4个地址空间,其中3个是PCI接口原有的,如内存、I/O和配置地址空间,另一外新PCI-Express接口新加的,它就是“信息空间”。PCI2.2标准中介绍不断变化的系统中断宣传的方法称之为“信息信号中断”(Message Signaled Interrupt,MSI)。这里特殊规格格式的内存写事物代替无边信号硬写,如中断、电源管理请求、复位等等有关信息方面。另一个PCI2.2标准的特殊循环,如中断响应也属于信息执行范畴。你可以把PCI-Express信息称之为“虚拟线”,因为它们的影响将消除现有执行平台中的广阔无限频带信号的排列。这几个地址空间类型的用途如下表所示。

| 不同地址空间的传输类型 | ||

| 地址空间 | 处理类型 | 基本用途 |

| 内存 | 读/写 | 处理来自或发送到内存中的数据 |

| I/O | 读/写 | 处理来自或发送到I/O节点中的数据 |

| 配置 | 读/写 | 设备配置或者设置 |

| 信息 | 基线/供应商定义/先进交换 | 处理从事件信号机制到通用目信息的所有信息 |

PCI Express使用数据包和层协议结构,而不需任何边带及旁路主流串行连接信号。层协议已经在数据通信中使用多年,它们允许在不同协议的功能区域中保持分离,而且可以不用做任何改动更新或者浓缩在其它不同层中。如新的处理类型可以包括在新的协议版本中,而不会影响下面的层,或者物理媒介可以被更换,而不会对更高层有大的影响。

下图9说明了PCI Express的3个协议层(处理层、数据链路层和物理层)在数据传输中的作用,数据流从一个设备的处理层发起,经过数据链路层,到物理的总线接口设备,然后通过相应的PCI Express数据电缆传输到另一设备的物理层设备,经过另一设备的数据链路层再传到处理层进行处理,第一层都代表一个协议栈。

图10显示了数据包在两个设备中传输的实际流程,高层数据包信息被压缩在低层封装包中,应用级数据最终在数据包的核心位置。处理层在端到端的数据传输中使用32位冗余校验码,在数据链路层是使用16位校验码的。处理层数据包头包括许多控制信息和端到端传输数据。

PCI Express处理层使用基于信任的流控制机制来确保接收设备有足够的缓存资源用于接受从发送端设备所传输的数据大小和类型。

图10

讲到数据处理,再来讲一下PCI Express总线接口中新的结构,那就是虚拟通道(Virtual lan)。类似于InfiniBand,PCI Express总线技术在每一个物理信道中也支持多点虚拟通道,理论上来讲每一个单物理信道中可以允许有8条虚拟通道信道进行独立通信控制。每个通信的数据包都定义不同的QoS,如图11所示。当数据包通过PCI Express组织传输时,在每个交换器或者链接终端,数据包的基本传输信息和传策略可以得到应用。传输信息在数据包包头,它包括3位代码,可以描述8个不同的传输信道。

图11

4. 软件层(Software Layer)

软件层被称为最重要的部分,因为它是保持与PCI总线兼容的关键。其目的在于使系统在使用PCI Express启动时,像在PCI下的初始化和运行那样,无论是在系统中发现的硬件设备,还是在系统中的资源,如内存、I/O空间和中断等,它可以创建非常优化的系统环境,而不需要进行任何改动。在PCI-Express体系结构中保持这些配置空间和I/O设备连接的规范稳定是非常关键的。事实上,在PCI-Express平台中所有操作系统在引导时都不需要进行任何编辑,也就是说在软件方面完全可以实现从PCI总线平稳过渡。

在软件响应时间模式方面,PCI-Express体系结构支持PCI的本地存储、共享内存模式,这样所有PCI软件在PCI-Express体系中运行都不需任何改变。当然新的软件可能包括新的特性。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多