电子网消息,Mentor, a Siemens business 今天宣布为 Calibre® nmPlatform、Analog FastSPICE™ (AFS™) Platform、Xpedition® Package Integrator 和 Xpedition Package Designer 工具推出几项增强功能,以支持 TSMC 的创新 InFO 集成扇出型高级封装和 CoWoS® 晶圆基底芯片封装技术。

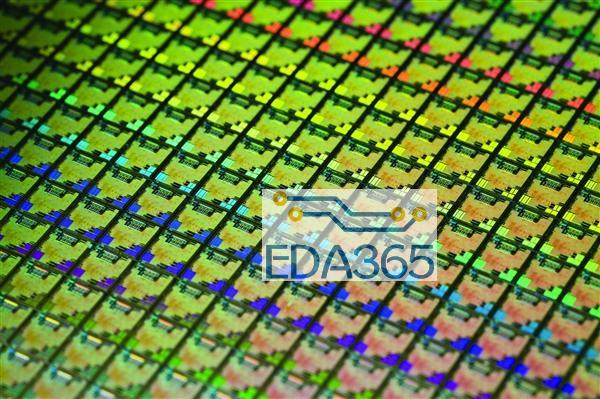

使用 TSMC InFO 和 CoWoS 3D 封装技术,客户能够在单个器件上混合使用多个硅片,达到比传统单片 IC 更高的集成度级别和容量。

在 Mentor Calibre 和 Xpedition 平台的基础上,Mentor 现在针对InFO推出了完整的从设计到封装的验证和分析套件。它的主要优势包括依托 Xpedition Package Integrator 的快速层次化设计原型环境,提供从设计到流片的快速流程;将 Xpedition Package Designer 和 Calibre Sign-off 验证套件集成。通过进一步协作,两条产品线实现了在Calibre 3DSTACK 和 Xpedition 工具之间的交互显示功能,结果可在 Calibre RVE™ 界面中查看。

TSMC 和 Mentor 还实现了 Mentor 热设计流程(包括 Mentor AFS 和 Calibre xACT™ 产品),以支持客户 InFO 设计的热相关仿真。

为了实现封装级别的跨芯片时序分析,Mentor 增强了 Xpedition Package Integrator 以支持网表功能,并且结合 Calibre xACT 寄生提取结果,帮助 InFO 和 CoWoS 设计人员验证时序要求。

对于所有设计流程而言,可靠性都是基本的要求。因此,TSMC 和 Mentor 开发了基于 Mentor Calibre PERC™ 可靠性平台的叠层芯片解决方案,适用于 TSMC 的 InFO 和 CoWoS 流程。这种新产品可满足Inter-die静电放电 (ESD) 分析需求。

TSMC 设计基础架构营销部高级总监 Suk Lee 说道:“我们与 Mentor 展开协作,为双方的共同客户提供支持,帮助他们快速利用TSMC 的 InFO 和 CoWoS 封装解决方案,并从中受益。“借助适用于 TSMC InFO 和 CoWoS 的 Mentor 设计套件,汽车、网络、高性能计算 (HPC) 和众多其他市场的客户可以达到全新的集成度级别。”

Mentor 副总裁兼 Design to Silicon 事业部总经理 Joe Sawicki 说道:“我们非常荣幸能够与长期合作伙伴 TSMC 携手合作,进一步改进和完善适用于 InFO 和 CoWoS 封装技术的 Mentor 设计解决方案。双方共同努力,将 3D-IC 打造成能够替代单片 IC 设计的可行主流解决方案,让越来越多的客户实现真正改变世界的卓越创新。”

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多