法国原子能署电子暨资讯技术实验室(CEA-Leti)宣布开发出单晶片(Monolithic) CoolCube 3D 设计途径,其目标在于成为第一个授权单晶片 3D 技术的单位之一。这项 CoolCube 3D 晶片技术计划由法国政府、IBM与高通(Qualcomm)等公司共同赞助合作。

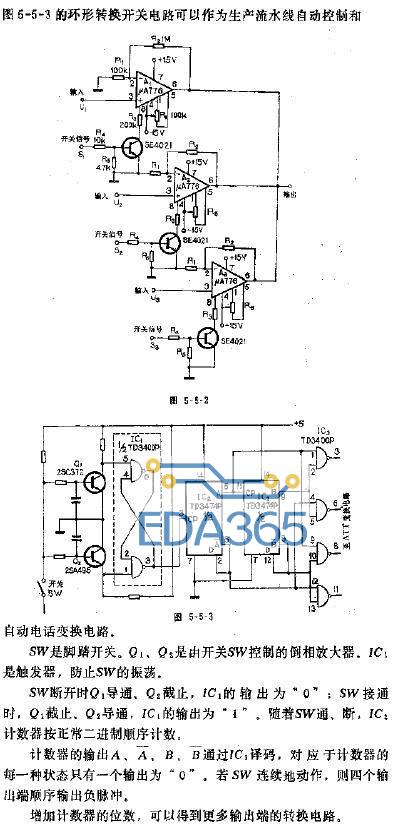

根据法国格勒诺布尔-阿尔卑斯大学(University of Grenoble Alpes)教授Olivier Billoint表示,单晶片 CoolCub 技术结合了传统的互补金属氧化物半导体(CMOS)处理技术、在中间层利用冷却 CMOS 制程步骤以及钨互连与穿孔的单层堆叠,以及顶层的铜金属。

“CoolCube 是单片3D晶片制造技术,底层采用传统的 CMOS 热制程,而内层则利用冷却的 CMOS 制程技术,”Billoint解释。

Billoint及其研究小组们认为,他们开发的 CoolCube 3D 晶片设计途径适用于传统的 CMOS 制程,但所具有的优点就像以 2D 平面晶片进展到下一个制程节点一样,从而延长了摩尔定律,只不过是以垂直的方向进展。

“我们利用传统的 2D CMOS 制程,在分层之间制造 3D 穿孔,所取得的优点就像以 2D 进展到更先进的制程节点一样,”Billoint表示,“我们预计这种途径可使功耗降低30%,性能提高40%,晶片面积更大幅缩减52%。”

CEA-Leti的CoolCube 3D途径是在底层采用传统的“热”CMOS制程,并以钨代替铜,然后在中间层采用冷却的CMOS制程,最后在顶层则以铜金属互连完成设计。

(来源:CEA-Leti)

CEA-Leti进行这项计划的时间已经长达八年,预计将在未来三年内完成设计原型。该研究机构期望能在2018年以前完成10nm制程的可用晶片。

然而,根据Billoint指出,在 3D 单晶片设计要能成为主流以前,还存在几个必须解决的问题。首先是如何决定哪一层必须在哪一层之上以及添加哪些功能,特别是发热的模组,如 CPU ——必须把这些特定模组放在单层或分成数层以便分别散热?

CoolCube 3D制程(蓝色)的优点包括缩减晶片面积、单次3D布线与分层间功率分配,而其挑战(红色)则在于层对层的单元布局最佳化以及功率最佳化。

(来源:CEA-Leti)

3D 单片技术的另一个重要问题是在许多节点存在立方体内部而无法以探针测试时如何实现设计?如何处理制程变异极端、特性化叠层热行为以及寻找解决方法等。

最后,CEA-Leti认为50/50的分层尺寸分布,并不一定都是最佳化的情况,因此目前正致力于打造一个可为每一分层实现最佳化的规则组合。

“为什么所有分层的尺寸应该相同?有些人会用不同的制程技术,有些会执行彼此不同的功能,而我们希望找到一种为每一分层尺寸实现最佳化的方法,”Billoint说。

关键字:CoolCube 3D技术

热门文章

更多

热门文章

更多