前言

在测控、仪器仪表、语音信号处理和图像通信领域中往往需要多处理器分工完成数字信号处理(DSP)算法和与外部系统的通信、控制、数据采集和人机接口功能。在多机系统中,CPU之间的通信常采用以下几种方式:(1)串行通信。这种方式相对简单,由于受到波特率的限制,在不同档次单片机之间需要通信业务大的场合得不到很好的通信效果。(2)并行通信。利用CPU的I/O功能在CPU之间增加缓冲器或锁存器实现双机通信。通信性能较串行通信有所提高,但仍然得不到理想的效果。(3)利用共享式存储器实现。DMA方式就是其中的一种,能够达到数据的高速传输,但不能同时访问存储器,CPU必须等待总线,而且有些CPU不支持DMA功能。另一种是利用多端口存储器,双口RAM和FIFO是常用的两种多端口的存储器,允许多CPU同时访问存储器,大大提高了通信效率,而且对CPU没有过多的要求,特别适合异种CPU之间异步高速系统中。因此,受到硬件设计者的青睐。

一、两种多端口存储器

1.双口RAM的仲裁控制

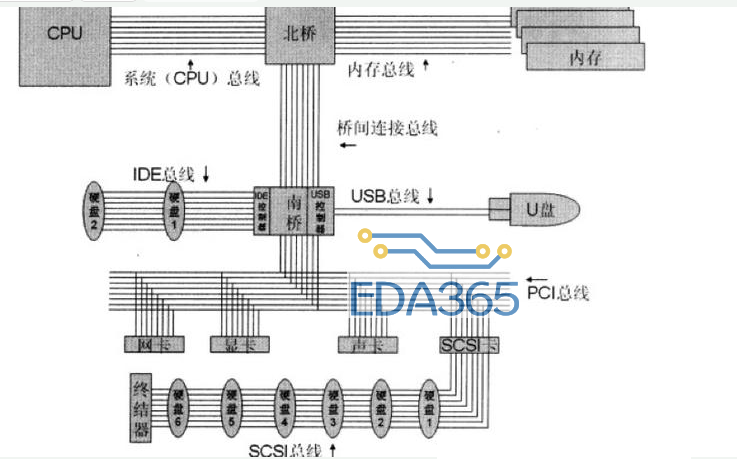

双口RAM是常见的共享式多端口存储器,以图1所示通用双口静态RAM为例来说明双口RAM的工作原理和仲裁逻辑控制。双口RAM最大的特点是存储数据共享。图1中,一个存储器配备两套独立的地址、数据和控制线,允许两个独立的CPU或控制器同时异步地访问存储单元。既然数据共享,就必须存在访问仲裁控制。内部仲裁逻辑控制提供以下功能:对同一地址单元访问的时序控制;存储单元数据块的访问权限分配;信令交换逻辑(例如中断信号)等。

(1)对同一地址单元访问的竞争控制

如果同时访问双口RAM的同一存储单元,势必造成数据访问失真。为了防止冲突的发生,采用Busy逻辑控制,也称硬件地址仲裁逻辑。图2给出了地址总线发生匹配时的竞争时序。,此处只给出了地址总线选通信信号先于片选脉冲信号的情况,而且,两端的片选信号至少相差tAPS――仲裁最小时间间隔(IDT7132为5ns),内部仲裁逻辑控制才可给后访问的一方输出Busy闭锁信号,将访问权交给另一方直至结束对该地址单元的访问,才撤消Busy闭锁信号,将访问权交给另一方直至结束对该地址单元的访问,才撤消Busy闭锁信号。即使在极限情况,两个CPU几乎同时访问同一单元――地址匹配时片选信号低跳变之差少于tAPS,Busy闭锁信号也仅输出给其中任一CPU,只允许一个CPU访问该地址单元。仲裁控制不会同时向两个CPU发Busy闭锁信号。

(2)存储单元数据块的访问权限分配

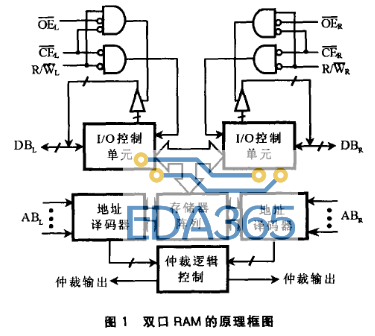

存储单元数据块的访问权限分配只允许在某一时间段内由1个CPU对自定义的某一数据块进行读写操作,这将有助于存储数据的保护,更有效地避免地址冲突。信号量(Semaphore,简称SEM)仲裁闭锁就是一种硬件电路结合软件实现访问权限分配方法。SEM单元是与存储单元无关的独立标志单元,图3给出了一个信号量闭锁逻辑框图。两个触发器在初始化时均使SEM允许输出为高电平,等待双方申请SEM。如果收到一方写入的SEM信号(通常低电平写入),如图3所示,仲裁电路将使其中一个触发器的SEM允许输出端为低电平,而闭锁另一个SEM允许输出端使其继续保持高电平。只有当先请求的一方撤消SEM信号,即写入高电平,才使另一SEM允许输出端的闭锁得到解除,恢复等待新的SEM申请。

(3)信令交换逻辑(signaling logic)

为了提高数据的交换能力,有些双口RAM采用信令交换逻辑来通知对方。IDT7130(1K容量)就是采用中断方式交换信令。利用两个特殊的单元(3FFH和3FEH)作为信令字和中断源。假设左端CPU向3FFH写入信令,将由写信号和地址选通信号触发右端的中断输出,只有当右端的CPU响应中断并读取3FFH信令字单元,其中断才被双口RAM撤消。

以上是双口RAM自身提供的仲裁逻辑控制,也可采用自行设计的仲裁协议。下面的实例将介绍这种方法。

2.FIFO的工作原理

FIFO(First In First Out)全称是先进先出的存储器。先进先出也是FIFO的主要特点。

20世纪80年代早期,FIFO芯片是基于移位寄存器的中规模逻辑器件。容量为n的这种FIFO中,输入的数据逐个寄存器移位,经n次移位才能输出。因此,这种FIFO的输入到输出延时与容量成正比,工作效率得到限制。

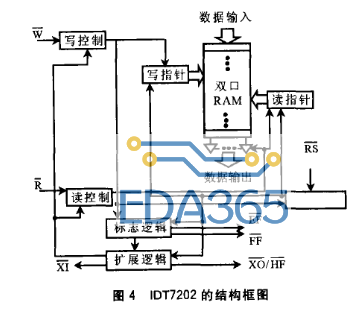

为了提高FIFO的容量和减小输出延时,现在FIFO内部存储器均采用双口RAM,数据从输入到读出的延迟大大缩小。以通用的IDT7202为例,结构框图如图4所示。输入和输出具有两套数据线。独立的读写地址指针在读写脉冲的控制下顺序地从双口RAM读写数据,读写指针均从第一个存储单元开始,到最后个存储单元,然后,又回到第一个存储单元。标志逻辑部分即内部仲裁电路通过对读指针和写指针的比较,相应给出双口RAM的空(EF)和满(FF)状态指示,甚至还有中间指示(XO/HF)。如果内部仲裁仅提供空和满状态指示,FIFO的传输效率得不到充分的艇。新型的FIFO提供可编程标志功能,例如,可以设置空加4或满减4的标志输出。目前,为了使容量得到更大提高,存储单元采用动态RAM代替静态RAM,并将刷新电路集成在芯片,且内部仲裁单元决定器件的输入、读出及自动刷新操作。

FIFO只允许两端一个写,一个读,因此FIFO是一种半共享式存储器。在双机系统中,只允许一个CPU往FIFO写数据,另一个CPU从FIFO读数据。而且,只要注意标志输出,空指示不写,满指示不读,就不会发生写入数据丢失和读出数据无效。

3.其他多端口存储器

以上只介绍了两种双端口存储器。随着电子工艺的飞速发展,出现了三端口及以上的存储器,并且在存储深度和宽度上得到很大发展,仲裁逻辑控制更加复杂;但多端口存储器源彼双端口存储器,基本更加复杂;但多端口存储器源自双端口存储器,基本工作原理入双端口存储器相似,这里不一一详述。

二、双口RAM实现数据采集系统

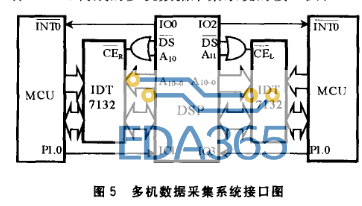

数字信号处理器(DSP)能实时快速地实现各种数字信号处理算法,而DSP的控制功能不强,可以采用8051单片机控制数据采集板,将采集的原始数据送给DSP处理并将处理结果传送给8位单片机。图5给出了利用1片数字信号处理器TMS320F206(以下简称DSP)和2片AT89C51单片机(以下简称MCU)构成多机数据采集系统接口图。

本系统采用两片CMOS静态双口RAM(IDT7132)实现MCU和DSP的数据双向传递。双口RAM作为DSP的片外数据存储器,即用外部数据存储器选通信号DS和高位地址信号经高速或门输出选通双口RAM的片选信号。这样可以利用DSP的重复操作指令(RPT)和数据存储器块移动指令(BLDD)减少数据传送时间,双口RAM的8位数据总线接在DSP的低8位。IDT7132的仲裁逻辑控制只提供Busy逻辑输出,而由于MCU无Busy功能,只能采用自行设计的软件协议仲裁方法。将双口RAM划分为两块:上行数据区(DSP接收MCU采集的数据区)和下地数据区(DSP输出处理结果区)。此处的上行数据区将远大于下行数据区。采用DSP的4个I/O口与MCU中断口和I/O口相连,并在数据区中规定一个信令交换单元。以DSP采集右端MCU上行数据为例,说明仲裁流程。

(1)初始化时,DSP置IO3为输出口,保持高电平,IO2为输入口(MCU使其初始化为低电平)。

(2)DSP需要采集MCU数据时,向右端IDT7132下行数据区的下行信令字单元(此处设为00H)写入需要取数的信令字,再向右端MCU发中断,置IO3为低电平,然后查询IO2等待MCU应答。

(3)MCU及时响应中断后,则先从IDT7132的下行数据区的下行信令字单元读取DSP请求信息,检测为DSP需要取数的下行信令。然后,向IDT7132上行数据区的上行信令字单元写入数据,准备好需要DSP取数据的信令(00H)或数据未准备好的信令(01H)。最后,向DSP发送应答信号,置IO2为高电平(此处高电平的持续时间不过长,只要DSP可以检测到即可)。

(4)DSP检测到IO2为高是平,表明MCU应答,立即读取IDT7132上行数据区的上行信令字单元。若为可以取数据的上行信令,则从IDT7132上行数据区取出采集数据,完成后,需要向右端MCU发送采集结束下行信令(01H);若为数据未准备好的上行信令(01H),则跳转至与左端MCU通信程序中。

以下是DSP部分采集右端MCU数据的部分代码:

rx1: splk #0020h,60h

out 60h,wsgr ;设置等待状态寄存器,指令周期为50ns;而IDT7132选用55ns,则需插入1个等待状态

splk #0000h,dn-sig ;向下行信令字单元写入00h(dn-sig表示下行信令字单元),通知MCU需要接收上行的语音数据

call int0gr ;向右端MCU发中断

reply:in 70h,iosr

bit 70h,12 ;检测IO3

bcnd reply,ntc ;IO3为低,返回reply,继续检测

lacl up-sig ;读上行信令字单元(up-sig表示下行信令字单元)到累加器中

sacl 70h

bit 70h,15

bcnd rx2,tc ;若为01H,表示MCU没有准备好,跳之与另一MCU通信rx2处;为00H,表示允许采集数据

mar *,ar1

lar ar1,#data-buf ;将目的数据块首地址存入ar1辅助寄存器

rpt #data-size ;重复下一条指令(data-size+1)次

bldd #up-data,*+

splk #0000h,dn-sig ;向下行信令字单元写入01h,表示采集数据结束,让出双口RAM上行数据区的使用权

call int0gr ;向右端MCU发中断

b rx2

RPT和BLDD是TMS320F206的高级指令,充分体现了DSP的流水线特点。RPT没有时间开销,它使下一条指令重复执行;BLDD是数据存储器间块移动指令,源和目的块不一定都要在片内或片外。当RPT和BLDD一起使用时,中断应该禁止,而且一旦流水线启动,BLDD就变成了单周期指令,如上述程序,DSP采集100Byte的数据,指令周期为50ns,一个等待状态周期则仅需50ns2100=10000ns=10μs,充分节省了采集时间,使DSP将更多的时间投入到算法中。

以下是产生中断子程序:

int0gr:in 70h,iosr ;读IO状态寄存器到70H单元中

lacl 70h

and #0fffbh

sacl 71h

out 71h,iosr;置IO2为低电平,下跳变触发INT0中断

call wait1 ;延时,低电平的持续时间需满足MCU接收中断的要求

lacl 70h

or #0004h

sacl 71h

out 71h,iosr ;恢复IO2为高电平

ret

三、FIFO的双向扩展和语音数据交换系统

用DSP实现语音压缩和解压算法得到了广泛的应用。例如,用TMS320LC549可以实现基于G.723.1压缩算法的全双工语音编解码器。G.723.1语音解码器可将输入的PCM编码压缩为6.3和5.3Kbps的语音数据,压缩出的语音数据是每30ms突发输出一帧。比如,6.3Kbps的速率,编解码器每30ms输出24Byte压缩语音帧(包括信令数据),同样,编解码器每30ms突发接收24Byte语音数据解压,输出PCM编码。为了实现语音数据的全双工实时交换,可采用双向FIFO设计交换系统。下面,以1片AT89C51(简称MCU)与2片TMS320LC549(简称DSP)实现语音数据双向交换为例,介绍FIFO的具体应用。其中DSP用于语音数据的压缩解压;MCU用于转发语音数据流和监控;FIFO用于CPU之间的数据缓冲。

首先,用2片单向FIFO IDT7202扩展为双向FIFO(也可使用专用的双向FIFO),如图6所示可以在A和B系统之间实现双向通信。

图7为语音双向交换的原理简图(图中未给出模拟话路和PCM编解码器等)。MCU分别通过两个双向FIFO与相应的DSP实现语音数据交换。MCU对双向FIFO的选通控制采用一片16V8GAL电路。DSP压缩完一帧用中断通知MCU取压缩的语音数据。

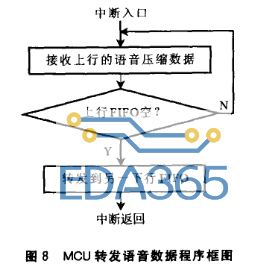

MCU在中断服务程序中接收压缩语音。图8给出了MCU的中断服务程序。如图8所吉,MCU分别在两个对等的中断服务程序中,从上行的FIFO接收上行的语音数据,然后转发给另一个下行的FIFO。DSP检测下行FIFO的空标志。若为空间,则从下行的FIFO中接收需要解压的语音数据,并对语音数据包解压回放。

由上可以看出,利用FIFO实现多机接口,硬件和通信流程简单,并且在实际的调试中,本系统的语音数据得到实时交换,没有出现语音帧丢失的情况,语音延时符合要求,可以实现全双工通信。

结束语

本文介绍了以双口RAM和FIFO为例,利用多端口存储器设计多机系统。现对双口RA几FIFO比较如下:(1)FIFO的仲裁控制简单,但其容量不如双口RAM。由于先进先出的特点,特别适合数据缓冲和突发传送数据。某些芯片的内部就集成小容量FIFO,例如,DSP的同步串口就集成两个FIFO,用于接收和发送数据缓冲。双口RAM的仲裁逻辑比FIFO复杂,但其容量较大。由于存储数据完全共享,适用于双机系统的全局存储器和大容量数据存储共享,例如大容量磁盘的数据缓存可采用双口RAM。(2)FIFO只给外部提供一个读和一个写信号,因此CPU用一个I/O地址便可读或写FIFO,使硬件趋于简单,给编程也带来一些方便,但CPU不能对FIFO内部的存储器进行寻址。双口RAM由于有两套地址线,使硬件较FIFO复杂,但允许CPU访问内部存储单元,因此CPU之间可以自己定主和分配数据块以及数据单元,使软件设计更加灵活。

在异种机系统设计中,利用双口RAM和FIFO能够实时、快速、灵活和方便地进行相互通信,得到满意的效果。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多