随着 DRAM 和 NAND 技术持续迈向更先进几何制程与多层次记忆体的道路,IC Insights密切观察有关 DRAM 和 NAND 供应商的最新动态,期望能提供更清楚的 DRAM / NAND发展蓝图。

在2014年中期,制造 NAND 快闪记忆体元件的最先进制程技术采用的是20nm以及更小的特征尺寸,而 DRAM 采用的制造技术还不到30nm。根据图1所示的制程技术蓝图显示,在2017年以前,最小特征尺寸为2D (平面)的NAND flash将会过渡到10-12nm,而 DRAM 则将迁移至20nm或更小的 DRAM 。

不过,IC Insights坦承,这样的发展态势还无加以定论,因为制造制程节点的定义并不明确,尤其是在企业试图在竞争中取得某种优势时,就很容易受到行销「游戏数字」的影响。

量产NAND flash和DRAM发展蓝图。

(来源:IC Insights)

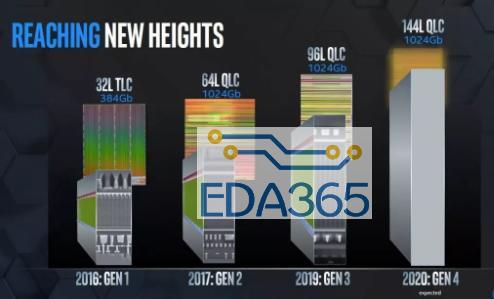

为了制造 NAND Flash ,2014年时已经加速量产15nm和16nm NAND 晶片了。三星(Samsung)是第一家最先量产 3D NAND 晶片的公司。该公司在2014年5月宣布开始量产采用32层记忆体单元的 V-NAND Flash 晶片。此外,在2013年,该公司已针对资料中心客户出货基于其第一代24层 V-NAND 技术的固态硬碟(SSD)。

从 2D 到3D NAND 记忆体全面转型的时机,将视 3D 成为更具成本效益选项之际而定,但这样的情况将会持续一段时间。甚至当达到成本的交叉点时, 2D 和 3D NAND 还可能共存好些年。

目前业界主要的 DRAM 制造商正以20nm级特征尺寸(20-29nm之间)进行量产制造。

如同 NAND flash 一样, DRAM 技术也正朝向以垂直方向整合电路的趋势发展。 3D DRAM 解决方案的例子之一是由HMC联盟开发的混合记忆体立方(HMC)。HMC联盟是由美光(Micron)和三星,以及包括Altera、ARM、IBM、Open-Silicon、海力士(SK Hynix)和赛灵思(Xilinx)等开发商共同组成。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多