功率 MOSFET 是便携式设备中大功率开关电源的主要组成部分。此外,对于散热量极低的笔记本电脑来说,这些 MOSFET 是最难确定的元件。本文给出了计算 MOSFET 功耗以及确定其工作温度的步骤,并通过多相、同步整流、降压型 CPU 核电源中一个 30A 单相的分布计算示例,详细说明了上述概念。

也许,今天的便携式电源设计者所面临的最严峻挑战就是为当今的高性能 CPU 提供电源。CPU 的电源电流最近每两年就翻一番。事实上,今天的便携式核电源电流需求会高达 60A 或更多,电压介于 0.9V 和 1.75V 之间。但是,尽管电流需求在稳步增长,留给电源的空间却并没有增加—这个现实已达到了热设计的极限甚至超出。

如此高电流的电源通常被分割为两个或更多相,每一相提供 15A 到 30A。这种方式使元件的选择更容易。例如,一个 60A 电源变成了两个 30A 电源。但是,这种方法并没有额外增加板上空间,对于热设计方面的挑战基本上没有多大帮助。

在设计大电流电源时,MOSFET 是最难确定的元件。这一点在笔记本电脑中尤其显著,这样的环境中,散热器、风扇、热管和其它散热手段通常都留给了 CPU。这样,电源设计常常要面临狭小的空间、静止的气流以及来自于附近其它元件的热量等不利因素的挑战。而且,除了电源下面少量的印制板铜膜外,没有任何其它手段可以用来协助耗散功率。

在挑选 MOSFET 时,首先是要选择有足够的电流处理能力,并具有足够的散热通道的器件。最后还要量化地考虑必要的热耗和保证足够的散热路径。本文将一步一步地说明如何计算这些 MOSFET 的功率耗散,并确定它们的工作温度。然后,通过分析一个多相、同步整流、降压型 CPU 核电源中某一个 30A 单相的设计实例,进一步阐明这些概念。

计算 MOSFET 的耗散功率

为了确定一个 MOSFET 是否适合于某特定应用,你必须计算一下其功率耗散,它主要包含阻性和开关损耗两部分:

PDDEVICE TOTAL = PDRESISTIVE + PDSWITCHING

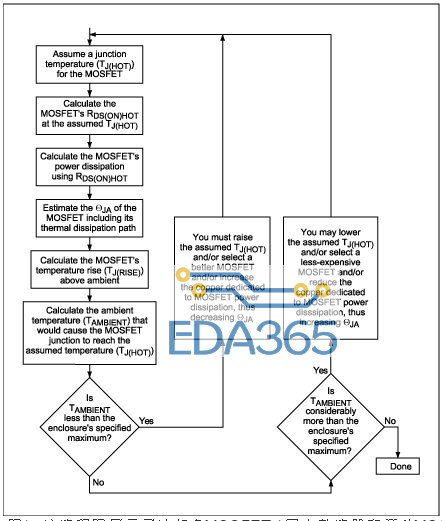

由于 MOSFET 的功率耗散很大程度上依赖于它的导通电阻(RDS(ON)),计算 RDS(ON)看上去是一个很好的出发点。但是 MOSFET 的 RDS(ON)与它的结温(TJ)有关。话说回来,TJ 又依赖于 MOSFET 的功率耗散以及 MOSFET 的热阻(ΘJA)。这样,似乎很难找到一个着眼点。由于功率耗散的计算涉及到若干个相互依赖的因素,我们可以采用一种迭代过程获得我们所需要的结果(图 1)。

图 1. 该流程图展示了选择各 MOSFET (同步整流器和开关 MOSFET)的迭代过程。在这个过程中,各 MOSFET 的结温为假设值,两个 MOSFET 的功率耗散和允许环境温度通过计算得出。当允许的环境温度达到或略高于我们所期望的机箱内最高温度时(机箱内安装了电源及其所驱动的电路),这个过程就结束了。

迭代过程始于为每个 MOSFET 假定一个结温,然后,计算每个 MOSFET 各自的功率耗散和允许的环境温度。当允许的环境气温达到或略高于电源及其所驱动的电路所在的机壳的期望最高温度时,这个过程便结束了。

有些人总试图使这个计算所得的环境温度尽可能高,但通常这并不是一个好主意。这样作就要求采用更昂贵的 MOSFET,在 MOSFET 下铺设更多的铜膜,或者要求采用一个更大、更快速的风扇产生气流—所有这些都不是我们所期望的。

从某种意义上讲,先假定一个 MOSFET 结温,然后再计算环境温度,这是一种逆向的考虑方法。毕竟环境温度决定了 MOSFET 的结温—而不是相反。不过,从一个假定的结温开始计算要比从环境温度开始容易一些。

对于开关 MOSFET 和同步整流器,我们可以选择一个最大允许的管芯结温(TJ(HOT))作为迭代过程的出发点。多数 MOSFET 的数据资料只规定了+25°C 下的最大 RDS(ON),不过最近有些 MOSFET 文档也给出了+125°C 下的最大值。MOSFET 的 RDS(ON)随着温度而增加,典型温度系数在 0.35%/°C 至 0.5%/°C 之间(图 2)。

图 2. 典型功率 MOSFET 的导通电阻的温度系数在 0.35%每度(绿线)至 0.5%每度(红线)之间

如果拿不准,可以用一个较差的温度系数和 MOSFET 的+25°C 规格(或+125°C 规格,如果有的话)近似估算在选定的 TJ(HOT)下的最大 RDS(ON):

RDS(ON)HOT = RDS(ON)SPEC [1 + 0.005 × (TJ(HOT) - TSPEC)]

其中,RDS(ON)SPEC 是计算所用的 MOSFET 导通电阻,TSPEC 是规定 RDS(ON)SPEC 时的温度。利用计算出的 RDS(ON)HOT,可以确定同步整流器和开关 MOSFET 的功率消耗,具体做法如下所述。

在下面的章节中,我们将讨论如何计算各个 MOSFET 在给定的管芯温度下的功率消耗,以及完成迭代过程的后续步骤(整个过程详述于图 1)。

同步整流器的功耗

除最轻负载以外,各种情况下同步整流器 MOSFET 的漏 - 源电压在打开和关闭过程中都会被续流二极管钳位。因此,同步整流器几乎没有开关损耗,它的功率消耗很容易计算。只需要考虑阻性损耗即可。

最坏情况下的损耗发生在同步整流器工作在最大占空比时,也就是当输入电压达到最大时。利用同步整流器的 RDS(ON)HOT 和工作占空比,通过欧姆定律,我们可以近似计算出它的功率消耗:

PDSYNCHRONOUS RECTIFIER = [ILOAD² × RDS(ON)HOT] × [1 - (VOUT/VINMAX)]

开关 MOSFET 的功耗

开关 MOSFET 的阻性损耗计算和同步整流器非常相似,也要利用它的占空比(不同于前者)和 RDS(ON)HOT:

PDRESISTIVE = [ILOAD² × RDS(ON)HOT] × (VOUT/VIN)

开关 MOSFET 的开关损耗计算起来比较困难,因为它依赖于许多难以量化并且通常没有规格的因素,这些因素同时影响到打开和关闭过程。我们可以首先用以下粗略的近似公式对某个 MOSFET 进行评价,然后通过实验对其性能进行验证:

PDSWITCHING = (CRSS × VIN² × fSW × ILOAD)/IGATE

其中 CRSS 是 MOSFET 的反向传输电容(数据资料中的一个参数),fSW 为开关频率,IGATE 是 MOSFET 的栅极驱动器在 MOSFET 处于临界导通(VGS 位于栅极充电曲线的平坦区域)时的吸收 / 源出电流。

一旦基于成本因素将选择范围缩小到了特定的某一代 MOSFET (不同代 MOSFET 的成本差别很大),我们就可以在这一代的器件中找到一个能够使功率耗散最小的器件。这个器件应该具有均衡的阻性和开关损耗。使用更小(更快)的 MOSFET 所增加的阻性损耗将超过它在开关损耗方面的降低,而更大(RDS(ON)更低) 的器件所增加的开关损耗将超过它对于阻性损耗的降低。

如果 VIN 是变化的,需要在 VIN(MAX)和 VIN(MIN)下分别计算开关 MOSFET 的功率耗散。MOSFET 功率耗散的最坏情况可能会出现在最低或最高输入电压下。该耗散功率是两种因素之和:在 VIN(MIN)时达到最高的阻性耗散(占空比较高),以及在 VIN(MAX)时达到最高的开关损耗(由于 VIN²项的缘故)。一个好的选择应该在 VIN 的两种极端情况下具有大致相同的耗散,并且在整个 VIN 范围内保持均衡的阻性和开关损耗。

如果损耗在 VIN(MIN)时明显高出,则阻性损耗起主导作用。这种情况下,可以考虑用一个更大一点的开关 MOSFET (或将一个以上的多个管子相并联)以降低 RDS(ON)。但如果在 VIN(MAX)时损耗显著高出,则应该考虑降低开关 MOSFET 的尺寸(如果是多管并联的话,或者去掉一个 MOSFET),以便使其开关速度更快一点。

如果阻性和开关损耗已达平衡,但总功耗仍然过高,有多种办法可以解决:

改变问题的定义。例如,重新定义输入电压范围。

改变开关频率以便降低开关损耗,有可能使用更大一点的、RDS(ON)更低的开关 MOSFET。

增加栅极驱动电流,有可能降低开关损耗。MOSFET 自身的内部栅极电阻最终限制了栅极驱动电流,实际上限制了这种方法的有效性。

采用一个改进技术的 MOSFET,以便同时获得更快的开关速度、更低的 RDS(ON)和更低的栅极电阻。

脱离某个给定的条件对 MOSFET 的尺寸作更精细的调整是不大可能的,因为器件的选择范围是有限的。选择的底线是 MOSFET 在最坏情况下的功耗必须能够被耗散掉。

热阻

下一步是要计算每个 MOSFET 周围的环境温度,在这个温度下,MOSFET 结温将达到我们的假定值(按照前面图 1 所示的迭代过程,确定合适的 MOSFET 来作为同步整流器和开关 MOSFET)。为此,首先需要确定每个 MOSFET 结到环境的热阻(ΘJA)。

热阻的估算可能会比较困难。单一器件在一个简单 PCB 上的ΘJA 测算相对容易一些,而要在一个系统内去预测实际电源的热性能是很困难的,那里有许多热源在争夺有限的散热通道。如果有多个 MOSFET 被并联使用,其整体热阻的计算方法,和计算两个以上并联电阻的等效电阻一样。

我们可以从 MOSFET 的ΘJA 规格开始。对于单一管芯、8 引脚封装的 MOSFET 来讲,ΘJA 通常接近于 62°C/W。其他类型的封装,有些带有散热片或裸露的导热片,其热阻一般会在 40°C/W 至 50°C/W (表 1)。

表 1. MOSFET 封装的典型热阻

注:同样封装类型的不同器件,以及不同制造商出品的相似封装的热阻各不相同,和封装的机械特性、管芯尺寸和安装及绑定方法有关。需仔细考虑 MOSFET 数据资料中的热信息。

可以用下面的公式计算 MOSFET 的管芯相对于环境的温升:

TJ(RISE) = PDDEVICE TOTAL × ΘJA

接下来,计算导致管芯达到预定 TJ(HOT)时的环境温度:

TAMBIENT = TJ(HOT) - TJ(RISE)

如果计算出的 TAMBIENT 低于机壳的最大额定环境温度(意味着机壳的最大额定环境温度将导致 MOSFET 的预定 TJ(HOT)被突破),必须采用下列一条或更多措施:

升高预定的 TJ(HOT),但不要超出数据手册规定的最大值。

选择更合适的 MOSFET 以降低 MOSFET 的功耗。

通过增加气流或 MOSFET 周围的铜膜降低ΘJA。

重算 TAMBIENT (采用速算表可以简化计算过程,经过多次反复方可选出一个可接受的设计)。另一方面,如果计算出的 TAMBIENT 高出机壳的最大额定环境温度很多,可以采取下述可选步骤中的任何一条或全部:

降低预定的 TJ(HOT)。

减小专用于 MOSFET 散热的覆铜面积。

采用更廉价的 MOSFET。

最后这几个步骤是可选的,因为在此情况下 MOSFET 不会因过热而损坏。不过,通过这些步骤,只要保证 TAMBIENT 高出机壳最高温度一定裕量,我们可以降低线路板面积和成本。

上述计算过程中最大的误差源来自于ΘJA。你应该仔细阅读数据资料中有关ΘJA 规格的所有注释。一般规范都假定器件安装在 1in²的 2oz 铜膜上。铜膜耗散了大部分的功率,不同数量的铜膜ΘJA 差别很大。例如,带有 1in²铜膜的 D-Pak 封装ΘJA 会达到 50°C/W。但是如果只将铜膜铺设在引脚的下面,ΘJA 将高出两倍(表 1)。

如果将多个 MOSFET 并联使用,ΘJA 主要取决于它们所安装的铜膜面积。两个器件的等效ΘJA 可以是单个器件的一半,但必须同时加倍铜膜面积。也就是说,增加一个并联的 MOSFET 而不增加铜膜的话,可以使 RDS(ON)减半但不会改变ΘJA 很多。

最后,ΘJA 规范通常都假定没有任何其它器件向铜膜的散热区传递热量。但在高电流情况下,功率通路上的每个元件,甚至是 PCB 引线都会产生热量。为了避免 MOSFET 过热,需仔细估算实际情况下的ΘJA,并采取下列措施:

仔细研究选定 MOSFET 现有的热性能方面的信息。

考察是否有足够的空间,以便设置更多的铜膜、散热器和其它器件。

确定是否有可能增加气流。

观察一下在假定的散热路径上,是否有其它显著散热的器件。

估计一下来自周围元件或空间的过剩热量或冷量。

设计实例

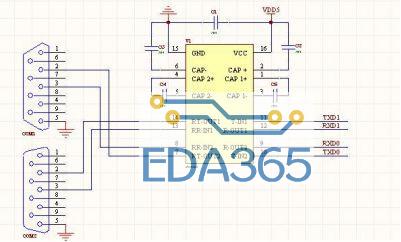

图 3 所示的 CPU 核电源提供 1.5V/60A 输出。两个工作于 300kHz 的相同的 30A 功率级总共提供 60A 输出电流。MAX1544 IC 驱动两级电路,采用 180°错相工作方式。该电源的输入范围 7V 至 24V,机壳的最大额定环境温度为+60°C。

图 3. 该降压型开关调节器中的 MOSFET 经由本文所述的迭代过程选出。板级设计者通常采用该类型的开关调节器驱动今天的高性能 CPU。

同步整流器由两片并联的 IRF6603 MOSFET 组成,组合器件的最大 RDS(ON)在室温下为 2.75mΩ,在+125°C (预定的 TJ(HOT))下近似为 4.13mΩ。在最大占空比 94%,30A 负载电流,以及 4.13mΩ最大 RDS(ON)时,这些并联 MOSFET 的功耗大约为 3.5W。提供 2in²铜膜来耗散这些功率,总体ΘJA 大约为 18°C/W,该热阻值取自 MOSFET 的数据资料。组合 MOSFET 的温升将接近于+63°C,因此该设计应该能够工作在最高+60°C 的环境温度下。

开关 MOSFET 由两只 IRF6604 MOSFET 并联组成,组合器件的最大 RDS(ON)在室温下为 6.5mΩ,在+125°C (预定的 TJ(HOT))下近似为 9.75mΩ。组合后的 CRSS 为 380pF。MAX1544 的 1Ω高边栅极驱动器可提供将近 1.6A 的驱动。VIN = 7V 时,阻性损耗为 1.63W,而开关损耗近似为 0.105W。输入为 VIN = 24V 时,阻性损耗为 0.475W 而开关损耗近似为 1.23W。总损耗在各输入工作点大致相等,最坏情况(最低 VIN)下的总损耗为 1.74W。

28°C/W 的ΘJA 将产生+46°C 的温升,允许工作于最高+80°C 的环境温度。若环境温度高于封装的最大规定温度,设计人员应考虑减小用于 MOSFET 的覆铜面积,尽管该步骤不是必须的。本例中的覆铜面积只单独考虑了 MOSFET 的需求。 如果还有其它器件向这个区域散热的话,可能还需要更多的覆铜面积。如果没有足够的空间增加覆铜,则可以降低总功耗,传递热量到低耗散区,或者采用主动的办法将热量移走。

结论

热管理是大功率便携式设计中难度较大的领域之一。这种难度迫使我们有必要采用上述迭代过程。尽管该过程能够引领板级设计者靠近最终设计,但是还必须通过实验来最终确定设计流程是否足够精确。计算 MOSFET 的热性能,为它们提供足够的耗散途径,然后在实验室中检验这些计算,这样有助于获得一个健壮的热设计。

APP下载

APP下载 登录

登录

热门文章

热门文章