verilog的三种端口类型分别是:

input输入端口;

output输出端口;

inout输入输出端口。这种大概有两种,但是就硬件上来说,其实都是一种,但是在某些情况下会把这个分为双向以及三态这两种。

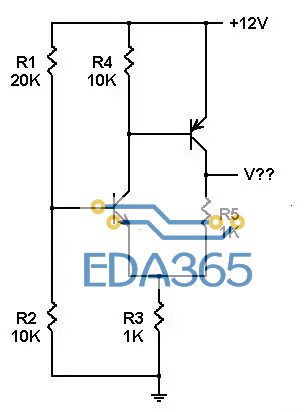

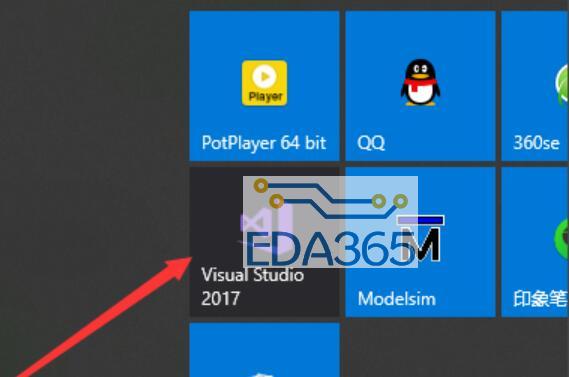

1、Verilog语言用于FPGA领域,在quartus ii中进行编辑,点击打开quartus ii,如下图所示。

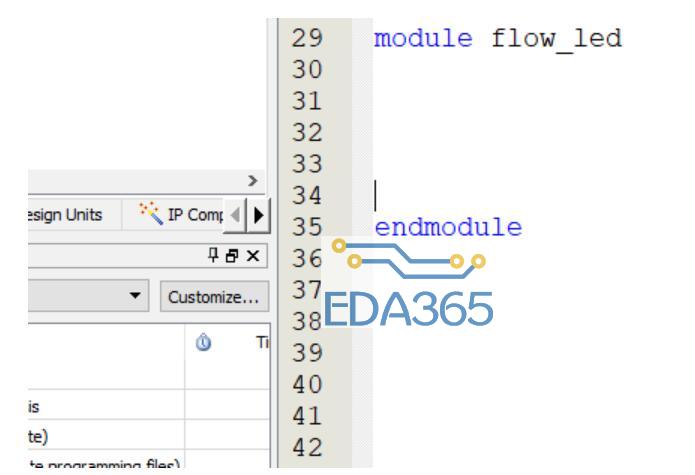

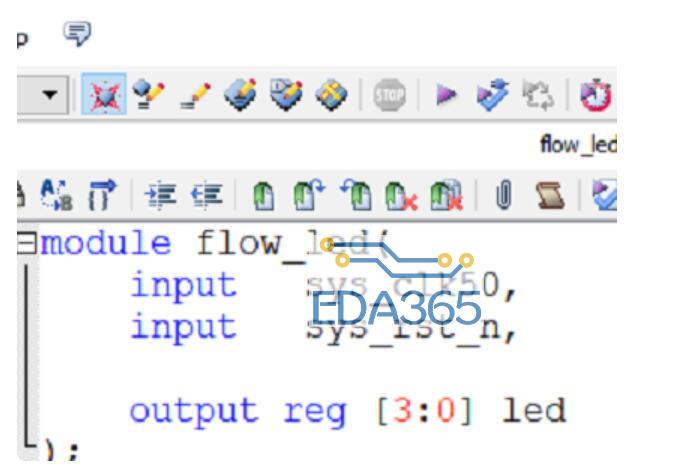

2、在Verilog中,代码以baimodule为一个模块,在.v文件头部和尾部分别输入module+模块名和endmodule即可,如下图所示。

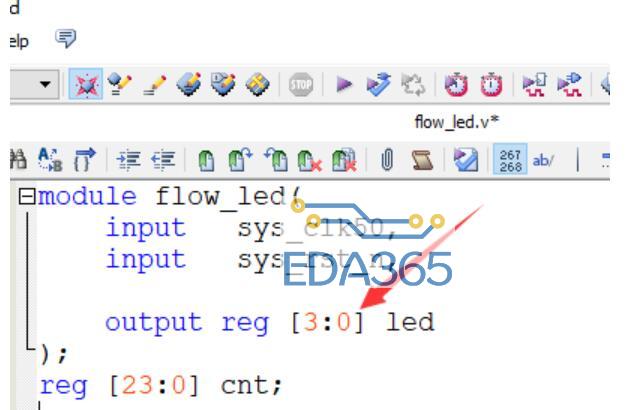

3、在module模块名后,需要对模块的输入输出端口进行定义,输入相应参数即可,如下图所示。

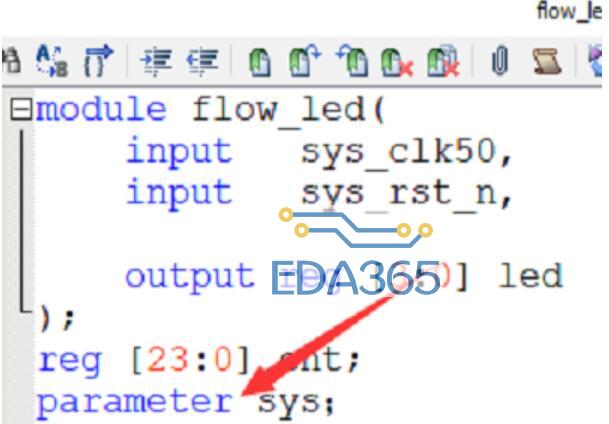

4、在Verilog中,有三种数据类型,一种是寄存器类型数据,一种是线网型,一种是参数型,参数型数据需要在前面加入parameter,点击即可,如下图所示。

5、在使用寄存器类型数据时,需要说明数据位宽,使用[n:0]表示,如下图所示。

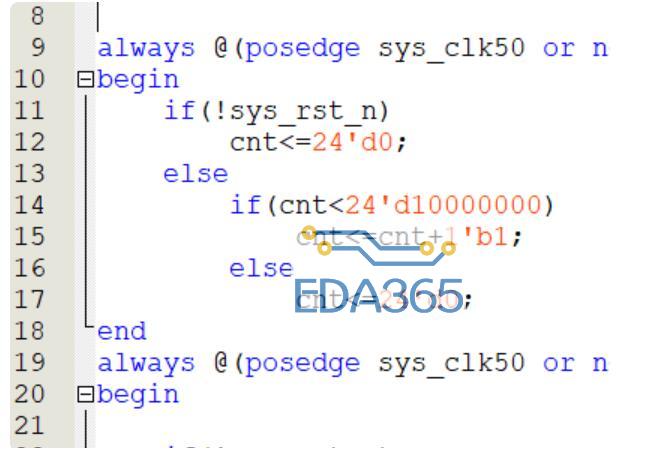

6、Verilog中,最常用的语句是always语句,要定义always语句的触发条件,常使用系统时钟,点击即可查看,如下图所示。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多