假设一百年或者几百年之后,回顾2018年到2019年的大国关系,未来的人们可能发明一个新词,或许就叫做芯片战争。虽然这种战争暂时还没听到枪炮声响和看到硝烟,但是对未来世界格局的深远影响,可能不亚于一场次级别的世界大战。这是因为围绕芯片这种国际商品而产生的交易额,是当今全球原油交易市场总额的数倍。围绕石油的大战已经不止一次,现在围绕芯片开始的激烈斗争,也将重构二十一世纪上半叶的基本世界格局。那么现在大家几乎天天听到芯片这个词。那么芯片到底是什么,为何设计和生产芯片成了一门高技术,对大多数人来说,恐怕都是半懂半不懂,或假装听得懂,也算一种基本态度。芯片说到底,其实就是一种微电路。那么什么又是电路?打开电脑的机箱,或者任何一种有程序化功能的电器内部,都会看到电路板。芯片就是一种极度微小但功能强大的微缩逻辑电路。

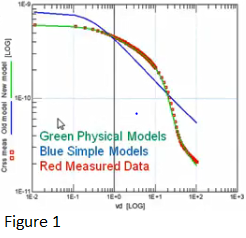

现代集成电路是由基尔比在1958年发明的。因此荣获2000年诺贝尔物理奖,实用集成电路的发明人是诺伊斯,因过世早而未能同时获奖,诺贝尔所有奖项只发给在世的人。集成电路可以把很大数量的微晶体管集成到一个小的纯硅的薄片上,这是一个巨大的进步。集成电路相对离散晶体管有两个主要优势:成本和性能。成本低是由于芯片把所有的组件通过照相平版技术,作为一个单位印刷,而不是在一个时间只制作一个晶体管。性能高是由于组件快速开关,消耗更低能量,因为组件很小且彼此靠近。现在已经进入纳米级,比如7纳米级的芯片,一平方厘米面积内就可以集成64个亿的微元件,已经接近物理规律的极限,再靠的更近,电子可能就直接穿透了电路之间的空间自然隔离,导致芯片电路自然失效了,这就是摩尔定律在微电子领域内的作用。

先进的集成电路是微处理器或多核处理器的核心,可以控制计算机到手机等一切电子设备。虽然设计开发一个复杂集成电路的成本非常高,但是当分散到通常以亿计的产品上,每个集成电路的成本最小化。最终利润就足够丰厚。

制作芯片的基础材料是单晶硅薄片。单晶硅是经过早年的多次试验后,认为是最合适的大规模制作集成电路的半导体材料。成为集成电路主流的基层。硅元素在地球地壳中含量很高,比如沙子水泥都含有大量的硅元素,但是能利用的是纯度极高的单晶硅,也就是提炼出不含亿分之一杂质的硅结晶,这种结晶体,直径越粗壮越好,越大的结晶,可以切割成直径越大的圆盘薄,在这种薄片上可以印刷更多的呈现长方形的小芯片。单晶硅圆盘的制作直径,是芯片加工企业的第一个技术高低的指标。过去研发无缺陷纯单晶硅晶体的方法就用了数十年的时间。制作芯片的基材,除了使用单晶硅,还有III-V族材料,比如砷化镓也可以。

现在流水线式的单晶硅芯片的制作完整过程包括芯片设计、晶片制作、封装制作、测试等几个环节,其中晶片制作过程尤为的复杂。首先是芯片设计,根据设计的需求,生成的“图样”。而制造芯片的原料是晶圆。晶圆的成分是纯硅,硅是由石英沙所精练出来的,晶圆便是硅加以纯化99.9999999%,接着是将这些纯硅制成硅晶棒,成为制造集成电路的石英半导体的材料,将其切片就是芯片制作具体所需要的晶圆。晶圆越薄,直径越大生产的成本越低,但对工艺就要求的越高。

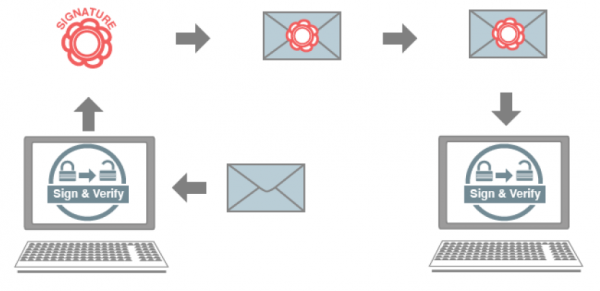

然后对晶圆进行涂膜,涂膜能抵抗氧化以及耐温能力,其材料为光阻的一种。再往后是晶圆的光刻显影、蚀刻。光刻工艺的基本流程。首先是在晶圆或衬底表面涂上一层光刻胶并烘干。烘干后的晶圆被传送到光刻机里面。光线透过一个掩模,把掩模上的图形投影在晶圆表面的光刻胶上,实现曝光,激发光化学反应。对曝光后的晶圆进行第二次烘烤,即所谓的曝光后烘烤,后烘烤是的光化学反应更充分。最后,把显影液喷洒到晶圆表面的光刻胶上,对曝光图形显影。显影后,掩模上的图形就被存留在了光刻胶上。如果看不明白这一点,就可以把晶圆看做老式胶卷照相机的显影工艺。

涂胶、烘烤和显影都是在匀胶显影机中完成的,曝光是在光刻机中完成的。匀胶显影机和光刻机一般都是联机作业的,晶圆通过机械手在各单元和机器之间传送。整个曝光显影系统是封闭的,晶圆不直接暴露在周围环境中,以减少环境中有害成分对光刻胶和光化学反应的影响。

这个复杂的过程使用了对紫外光敏感的化学物质,即遇紫外光则变软。通过控制遮光物的位置可以得到芯片的外形。在硅晶片涂上光致抗蚀剂,使得其遇紫外光就会溶解。这时可以用上第一份遮光物,使得紫外光直射的部分被溶解,这溶解部分接着可用溶剂将其冲走。这样剩下的部分就与遮光物的形状一样了,而这效果正是所要的。

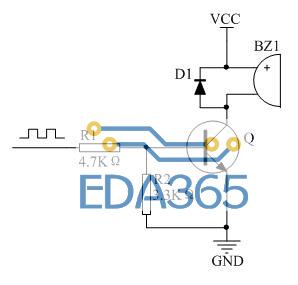

下一个工序是掺加杂质,将晶圆中植入离子,生成相应的P、N类半导体。具体工艺是从硅片上暴露的区域开始,放入化学离子混合液中。经过上面的几道工艺之后,晶圆上就形成了一个个格状的晶粒。通过针测的方式对每个晶粒进行电气特性检测。将制造完成晶圆固定,绑定引脚,按照需求去制作成各种不同的封装形式。经过上述工艺流程以后,芯片制作就已经全部完成了,最后步骤是将芯片进行测试、剔除不良品,最后包装上市。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多