【导读】EMC设计中,电容应用非常广泛,主要用于构成各种低通滤波器或用作去耦电容和旁路电容。本文根据EMC设计原理和不同结构电容的特点,讨论了在EMC设计中电容的应用。

EMC设计中,电容应用非常广泛,主要用于构成各种低通滤波器或用作去耦电容和旁路电容。在EMC设计中,正确选择与使用电容,可以解决许多EMI问题。若电容的选择或使用不当,则可能达不到预期的目的,甚至会加剧EMI程度。 本文根据EMC设计原理和不同结构电容的特点,讨论了在EMC设计中电容的应用。

1 电容的自谐振频率

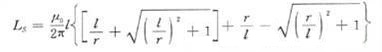

实际的电容都有寄生电感Ls。Ls的大小基本上取决于引线的长度,对圆形、导线类型的引线,上''的典型值为10nH/cm[3]。典型的陶瓷电容的引线约有6 mm长,会引入约15nH的电感''"。引线电感也可由下式估算[4]:

其中:/和r分别为引线的长度和半径。 寄生电感会与电容产生串联谐振,即自谐振,在自谐振频率fo处,去耦电容呈现的阻抗最小,去耦效果最好。但对频率f高于f/o的噪声成份,去耦电容呈电感 性,阻抗随频率的升高而变大,使去耦或旁路作用大大下降。实践中,应根据噪声的最高频率fmax来选择去耦电容的自谐振频率f0,最佳取值为 fo=fmax。 但是,一些资料上只是从电容的寄生电感的角度给出了自谐振频率fo的资料。实际上,去耦电容的自谐振频率不仅与电容的寄生电感有关,而且还与过孔的寄生电 感[5]、联结去耦电容与芯片电源正负极引脚的印制导线的寄生电感[6.7]等都有关系。如果不注意这一点,查得的资料或自己的估算往往与实际情况相去甚远。 实践中,一般是先确定去耦电容的结构(电容的寄生电感与其结构关系密切),再用试验的方法确定容量。

2 电容结构的选择

从理论上讲,电容的容量越大,容抗就越小,滤波效果就越好。一些人也有这种习惯认识。但是,容量大的电容一般寄生电感也大,自谐振频率低(如典型的 陶瓷电容,0.1 uF的fo=5MHz,0.01ulF的fo=15MHz,0.001uF的f0=50MHz),对高频噪声的去耦效果差,甚至根本起不到去耦作用。分立 元件的滤波器在频率超过10MHz时,将开始失去性能。元件的物理尺寸越大,转折点频率越低。这些问题可以通过选择特殊结构的电容来解决。 贴片电容的寄生电感几乎为零,总的电感也可以减小到元件本身的电感、通常只是传统电容寄生电感的1/3~1/5,自谐振频率可达同样容量的带引线电容的2 倍(也有资料说可达10倍),是射频应用的理想选择。

传统上,射频应用一般选择瓷片电容。但在实践中,超小型聚脂或聚苯乙烯薄膜电容也是适用的,因为他们的尺寸与瓷片电容相当。 三端电容能将小瓷片电容频率范围从50MHz以下拓展到200MHz以上,这对抑制VHF频段的噪声是很有用的。要在VHF或更高的频段获得更好的滤波效 果,特别是保护屏蔽体不被穿透,必须使用馈通电容。

3 电容容量的选择

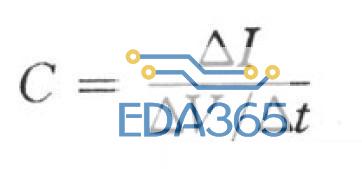

在数字系统中,去耦电容的容量通常按下式估算: 其中:/xl为瞬变电流;AV为逻辑器件允许的电源电压变

此外,当电源引线比较长时,瞬变电流会引起较大的压降,此时就要加容纳电容以维持器件要求的电压值。

4 去耦电容的安装方式与PCB设计

安装去耦电容时,一般都知道使电容的引线尽可能短。但是,实践中往往受到安装条件的限制,电容的引线不可能取得很短。况且,电容引线的寄生电感只是 影响目谐振频率的因素之一,自谐振频率还与过孔的寄生电感、相关印制导线的寄生电感等因素有关。一味地追求引线短,不仅困难,而且根本达不到目的。 这说明要保证去耦效果,在PCB设计时,就要考虑相关问题。设计印制导线时,应使去耦电容距离芯片电源正负极引脚尽可能近(当然电容引线要尽可能短)。设 计过孔时应尽量减小过孔的寄生电感。

APP下载

APP下载 登录

登录

热门文章

热门文章