本文采用的DC-DC降压变换器电路结构

本文采用的DC-DC降压变换器结构采用同步校正器代替传统的二极管,极大地提高了DC-DC降压变换器的效率,可达到95%左右。芯片的输入电压位于2.7V至5V之间,可工作在以下四种模式:固定频率的强制PWM模式,同步PWM模式,idle模式,关断模式。

限流比较器的设计

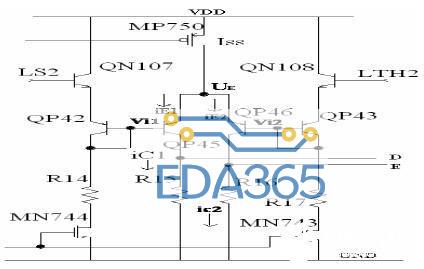

比较器输入级的设计

比较器输入级为射级耦合的差分输入级。

图1比较器的输入级

由上图可知,

(1)

(2)

则iC1可以近似为

(3)

同理

(4)

可求得差分跨导为:

(5)

在室温下,TV=26mV,所以运放跨导等于

(6)

此外,电阻R15,R16作为运放负载,可得出放大器输入级增益表达式如下:

(7)

比较器中间级

比较器中间级由D,E输入,A输出。MP724,MP725的作用是减小A点电压的变化幅度,使得比较器具有较短的瞬态响应时间和较快的速度。

现在计算折叠共源共栅运放的小信号电压增益,因为|Av|=GmRout,我们必须计算Gm和Rout,而

(8)

(9)

所以,V2A表达式如下:

(10)

图2比较器中间级

比较器输出级

比较器的输出级(ActiveLoadinverter)由A输入,B输出(图3),进一步提高放大器的增益,

(11)

因此,放大器总的增益AV表达式如下:

(12)

图3PFM限流比较器电路图

限流比较器电路图

综合前面比较器输入级,输出级,中间级的设计,可得出图3所示的PFM限流比较器电路图。当功率管导通时,对电感电流充电,使得电感电流上升,同时功率管的漏端电压下降,电流采样电路通过采样导通功率管的漏端电压,把采样得到的电压LS2,LTH2输入到PFM限流比较器,当功率管的漏端电压下降到一定程度,使得LS2达到PFM限流比较器门限LTH2时,比较器输出高电平至控制逻辑模块,从而使芯片进入PFM工作模式以延长电池寿命。

限流比较器的仿真

我们采用HSPICE对图3所示的电路进行了比较器功能的模拟,由图4可见当电感电流上升时,采样得到的电压LS2下降,当功率管的漏端电压下降到一定程度,使得LS2达到PFM限流比较器门限LTH2时,比较器输出高电平至控制逻辑模块,从而使芯片进入PFM工作模式以延长电池寿命。此外,比较器延迟70nS。

图4PFM限流比较器的仿真

结束语

本文成功地设计出一款应用到DC/DC芯片上的PFM限流比较器,并通过HSPICE进行了仿真。结果表明:电路结构简单,功耗低,响应速度快,完全满足新一代DC/DC产品的要求,且预计投入市场之后将获得上百万元的效益。

本文作者创新点:本文采用的DC-DC降压变换器结构采用同步校正器代替传统的二极管,极大地提高了DC-DC降压变换器的效率,可达到95%左右。基于该DC-DC降压变换器结构设计了一个新颖的基于Step-DownPWM电源管理芯片的PFM限流比较器电路,在轻载时使芯片进入PFM工作模式,因此能够延长电池寿命并且大幅度的提高Step-DownPWM电源管理芯片的效率。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多