在一块PCBA中,我们所看到的器件 多的一定是电阻。如果说芯片是电路的大脑,那么电阻便是连接各肢体的神经元。在高速电路设计中电阻的应用主要有六点。

1、限流作用

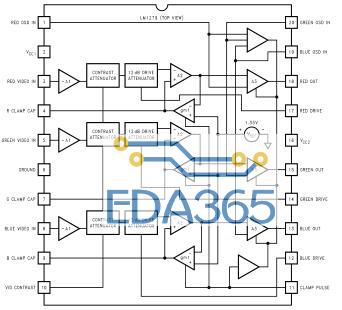

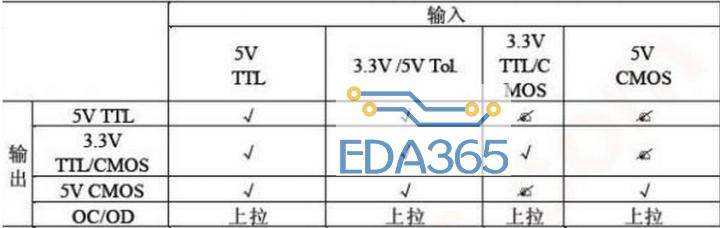

在高速电路中同时存在很多TTL芯片、MOSFET芯片、IGBT芯片、那么芯片之间驱动兼容便尤为重要。当MOSFET电平驱动TTL芯片时,便需要加限流电阻。而相反则需要增加电源以增加驱动电流(设计到电平转换电路)。

“各种不同IC之间的接口驱动要求”各种不同IC之间的接口驱动要求

2、电阻

2.1、在高速电路中我们所需要的的采样电路、分压电路、反馈电路等由电阻组成时,我们需选用1% 的电阻。

2.2、由于芯片的AD口都会存在上拉或者下拉电阻,此时情更需注意电阻值的选择,使得测得的芯片AD口测得的电压误差小(涉及到MCU的AD口电阻匹配问题)

3、阻抗匹配

很多高速信号线上,如特性阻抗为75欧姆的CVBS信号线、特性阻抗为100欧姆的LVDS数据信号线、特性阻抗为90欧姆的USB高速数据线上,在信号传输的过程中,路径的每一步都有相应的瞬态阻抗,如果沿着互联线传输的电信号感到的瞬态阻抗发生变化,那么一部分将继续走下去,而另外一部分将反射后源端。

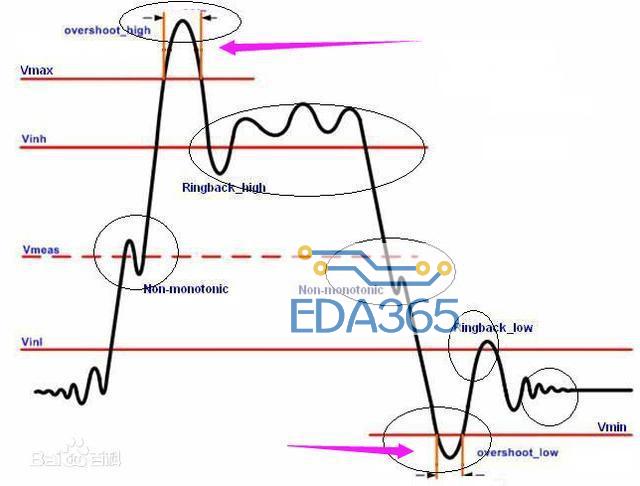

由于各个信号线上所需要的特性阻抗不一致,且信号源的阻抗不匹配。当源内阻小于传输线内阻时将出现振铃,也就是过冲,过载传输线。过大的过冲往往会损坏器件。而如果源内阻大于传输线阻抗时,便会出现欠冲,这会引起电路逻辑处于不确定状态,可能导致误判或信号丢失。

“信号线的过冲与欠冲现象”信号线的过冲与欠冲现象

此时便需要串联电阻、并联电阻、上拉电阻、下拉电阻等手段改善阻抗匹配情况。减少高速信号线上的由于阻抗匹配失配的情况下造成的信号反射等情况。

“端接电阻不仅可以限流还可以改善信号线阻抗匹配”端接电阻不仅可以限流还可以改善信号线阻抗匹配

4、滤除高频噪声

当高速信号线之间串联电阻后,电阻便和信号线间的分布电容及负载的输入电容组成RC电路,降低信号边沿的陡峭程度。此举可以消除信号线的高频噪声,改善EMC。

例如,USB驱动器和USB线的阻抗匹配必须在USB D 和D-上串联电阻,串联电阻的要求为Rs R串=USB线特性阻抗;

以下分别为串联3ohm、51ohm、68ohm眼图,RTmean和FTmean为上升和下降时间的平均值。

“过冲较大”过冲较大

“没有过冲”没有过冲

“电路参数</strong” width="600">电路参数

注意:若电阻较大会造成边沿的陡峭程度过低,此时会造成高速数据由于建立时间与保持时间不足或裕量不够而丢失数据,从数据眼图上看即可区别。

“R串=0ohm眼图”R串=0ohm眼图

“R串=33ohm眼图”R串=33ohm眼图

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多