Cadence 设计系统公司日前宣布,中芯国际集成电路制造有限公司(以下简称“中芯国际”)采用了 Cadence(R) Litho Physical Analyzer 与 Cadence Litho Electrical Analyzer,从而能够更准确地预测压力和光刻差异对65和45纳米半导体设计性能的影响。

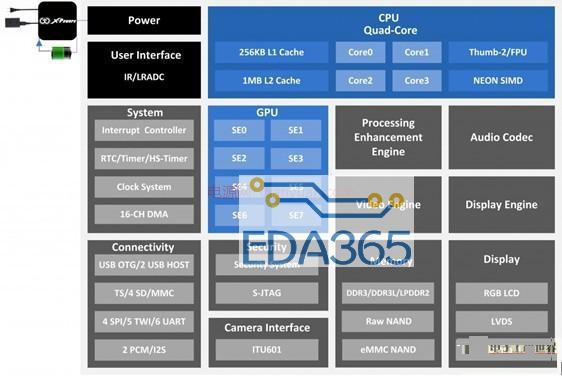

此前单个单元和库的电气行为可在一个单独的环境中进行预先标示,该单独环境在给定的、基于目标制程技术的设计中使用时可保持一致性。在65及更小纳米,单元的每次放置都产生了自己的一套物理和电气差异,这些差异与邻近的单元或环境有关。这种“与环境有关的差异”已成为关键的问题,可导致芯片设计失败。Cadence Encounter(R) Digital Implementation System (EDI) 无缝地整合了 Litho Physical Analyzer 与 Litho Electrical Analyzer,可在全芯片实现之前进行严苛的、与环境有关的单元物理与电气签收。该流程利用了模型化的物理与电气可制造性 (DFM) 技术,可提高标准单元库、知识产权 (IP) 核、及全芯片的品质和可靠性,从而提高完整芯片的制造成品率。

“在65和45纳米上必须解决物理和电气差异,这需要一种整体性的方法,它要始于单元级别,并考虑到设计的整个环境,”中芯国际设计服务中心副总裁刘明刚表示,”通过 Cadence 的 DFM 流程,我们能够分析单元和 IP 差异,并能对它们在真实硅片中的性能进行精确建模。 通过标示和减少差异,我们的客户将能减少防护带并制出更高品质的硅片。该解决方案还能实现近线性可扩展性,而这对于全芯片电气 DFM 验证流程来说是必需的。

Cadence 已开发出业界最完整的设计侧 DFM 预防、分析和签收方法学之一,并包括 Encounter Digital Implementation System 设计侧优化。它也被用于32和28纳米库的差异建模。“快速、精确、与环境有关的单元光刻与压力效应差异建模,对实现65纳米及以下节点实现有价值生产设计非常关键,”Cadence 实现集团研发副总裁徐季平表示。“众多一次硅片成功已证明了高容量半导体设计 DFM 分析工具的价值。”

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多