1 PROTEUS软件简介

PROTEUS是来自英国公司的工具软件,在全球广泛使用。和其它工具相比,这款软件的最大特点就在于它能够模拟单片机。可以直接在基于原理图的虚拟原型EDA上编程,并实现软件源码级的实时调试。还能看到运行后输入输出的效果。但是现在大家都只注意到PROTEUS对单片机的仿真和如何与Keil进行关联调试,其实PROTEUS还能够进行PLD的电路仿真。

PLD(可编程逻辑器件)是一种数字集成电路的半成品,在其芯片上按一定排列方式集成了大量的门和触发器等基本逻辑元件,使用者可利用某种开发工具对其进行加工,即按设计要求将这些片内的元件连接起来,使之完成某个逻辑电路或系统的功能,成为一个可在实际电子系统中使用的专用集成电路。

一般的PLD设计软件只能进行PLD芯片的时序逻辑仿真,而PROTEUS能进行PLD的电路仿真,可以模拟设计的PLD芯片在电路中实际运行的情况。

我们通过使用GAL16V8设计一个在单片机系统里常用的三八译器,然后在PROTEUS中通过观察GAL16V8中三八译码器的输入与输出的对应关系来完成PLD的电路仿真。

2. PLD的设计

首先用Protel 99SE完成PLD的设计。

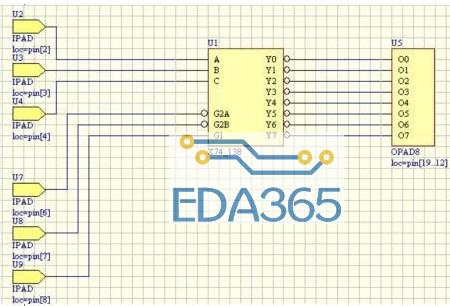

完成后的PLD原理图如下所示:

图1画好的PLD原理图这是一个3-8译码器的PLD文件。输入信号为目标元件的2、3、4三个脚,输出信号为目标元件的12-19脚,6-8脚为使能控制端。

Protel 99SE的PLD原理图的设计与普通原理图相同,但有几点是需要注意:

生成PLD元理图后,在原理图中自动加入了两个PLD的元件库(PLD_Devices.lib、PLD_Symbols.lib),PLD的电路图绘制必需使用这两个库中的元件。

绘制PLD原理图时,必须放置输入/输出端口(输入:IPAD、输出:OPAD、输入/输出:IOPAD)元件,这些元件所指定的引脚代表着目标器件的引脚。

在输入/输出端口元件放置好后,必须对其进行编号,还要指定该端口元件所对应连接的目标器件的引脚号。

完成PLD原理图后,选择[PLD]/[Compile]进行编译,生成各种格式的文件:

图2编译生成的各种文件打开生成的。jed文件,点击右键,在弹出的窗口中选择[Export…]项,选择。jed文件的输出目标地址。

至此就完成了PLD文件的设计。

3 Proteus对PLD的仿真

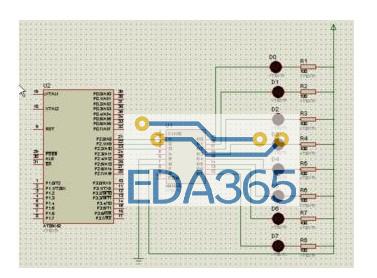

启动Proteus,绘制好电路图。

图3 Proteus仿真电路图电路中LED显示采用低电平时LED点亮的显示方式。电路中I1-I3为GAL16V8输入端口,端口为高电平时为1,低电平时为0,IO0-IO7为输出端口,输出端口为:LED灯亮时端口输出低电平0,熄灭时为高电平1.为了使PLD元件能仿真,还必须在电路中将编译的。jed文件加入PLD元件中:将鼠标移到U1(16V8)中,右击,选择元件,然后左击,调出“元件的属性”对话框,在属性对话框中,在窗口中的“JEDEC Fuse Map File:”中加入。jed文件:

图4 16V8元件属性由前面PLD的设计可得3-8译码器的真值表:输入信号输出信号I3 I2 I1 IO7 IO6 IO5 IO4 IO3 IO2 IO1 IO0 0 0 0 1 1 1 1 1 1 1 0 0 0 1 1 1 1 1 1 1 0 1 0 1 0 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 0 1 1 1 1 0 0 1 1 1 0 1 1 1 1 0 1 1 1 0 1 1 1 1 1 1 1 0 1 0 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1表1 3-8译码器真值表为了观察16V8的输入与输出的对应关系,我们在AT89C52的程序(程序见附录)中将与I3、I2、I1相连的P2_2、P2_1、P2_0三个端口按真值表中的顺序依次改变,观察LED灯是否由IO0至IO7依附点亮。

将单片机的程序加入AT89C52后,在Proteus中点击Play键观看电路仿真结果:当输入端的I1、I2、I3值按程序设定按真值表中的000—111依附改变时,输出端对应LED灯按真值表中的对应关系由IO0至IO7依次点亮,如下图。说明PLD器件16V8设计的三八译码器译码正确。

图5译码电路对应输入/输出截图

4.结语

单片机与PLD的结合是当前嵌入式设计经常采用一的种方式。但如果要进行硬件电路测试和系统调试则比较麻烦,因为要进行这两个过程必须在电路板制作完成、元器件焊接完毕之后进行。而电路板的制作、元器件的安装、焊接是费时费力的,如果采用作为单片机系统的仿真工具PROTEUS进行单片机和PLD的仿真,则不用制作具体的电路板也能够完成以上工作。在使用PROTEUS运行系统虚拟开发成功之后再进行实际制作,可以直观得观察电路的运行情况,提前发现设计的错误,可以极大的提高开发效率、降低开发成本、提高开发速度。

程序附录:

#include sbit P2_0=P2^0;sbit P2_1=P2^1;sbit P2_2=P2^2;

void delaytime(int count);void main(void)

{ while(1)

{ P2_2=0;P2_1=0;P2_0=0;delayTIme(500);P2_2=0;P2_1=0;P2_0=1;delayTIme(500);P2_2=0;P2_1=1;P2_0=0;delayTIme(500);P2_2=0;P2_1=1;P2_0=1;delayTIme(500);P2_2=1;P2_1=0;P2_0=0;delaytime(500);P2_2=1;P2_1=0;P2_0=1;delaytime(500);P2_2=1;P2_1=1;P2_0=0;delaytime(500);P2_2=1;P2_1=1;P2_0=1;delaytime(500);

}

void delaytime(int count)

{

int j,k;

while(count-- !=0)

{

for(j=0;j《10;j++)

for(k=0;k《72;k++)

;

}

}

责任编辑:pj

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多