概述

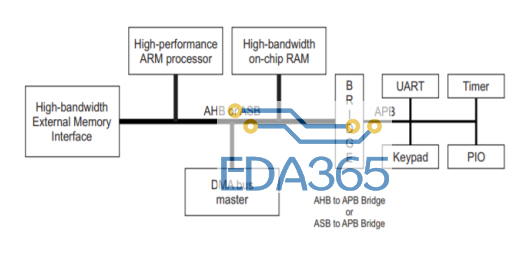

高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。

在Zynq器件应用Vivado HLS IP

这里集成了HLS IP和由HLS创建的软件驱动,目的是控制在Zynq器件上实现的IP设计。

Step 1: 创建Vivado HLS IP Block

脚本完成时,会生成vhls_prj文件,里面包含HLS IP,下面介绍Vivado HLS IP blocks如何被集成到使用IP Integrator的Zynq器件中。

Step 2: 创建 Vivado Zynq Project

1.打开vivado 2016.3,点击Create New Project,选择Using_IP_with_Zynq\lab1路径,下一步在Project Type页面选择RTL Project和Do not specify sources at this time

然后在Boards下选择ZYNQ-7 ZC702 Evaluation Board,最后点击Finish。

Step 3:将HLS IP 添加到 IP Catalog

在Flow Navigator窗口点击IP Catalog,然后点击IP Settings,在IP部分里Add Repository,选择Using_IP_with_Zynq\lab1\hls_macc\vhls_prj\solution1\impl\ip,这样就把HLS_macc这个HLS IP添加进IP目录中。

Step 4: 创建一个IP Integrator Block系统的设计

1.在Flow Navigator窗口点击Create Block Design,将design name改为Zynq_Design,然后添加ZYNQ7 Processing System这个IP,然后双击ZYNQ IP打开Re-customize IP窗口,在Presets选择ZC702,在Page Navigator窗口点击MIO Configuration,展开Application Processor Unit,去掉Timer 0,最后在Page Navigator窗口点击Interrupts,勾选并展开Fabric Interrupts,选择IRQ_F2P[15:0]

2.点击标题上的Run Block Automation,选择processing_system7_0,去掉Apply Board Presets,然后将hls_macc IP添加进设计,然后点击Run Connection Automation,选择/hls_macc_0/S_AXI_HLS_MACC_PERIPH_BUS,这样HLS IP就自动连接到 Zynq器件上的M_AXI_GP0 接口,然后连接hls_macc_0的interrupt端口和PS7的IRQ_F2P[0:0]端口。

3.选择Address Editor,确定hls_macc_0外部已经分配到主地址范围,如果没有,就点击Auto Assign Address

最后是Validate Design,成功通过后,save the Block Design。

Step 5: 实现系统

在进一步系统设计之前,必须生成一个source 和HDL wrapper来作为综合和实现顶层函数。

1.Flow Navigator窗口里选择Project Manager,在Zynq_Design右击选择Generate Output Products,然后选择Generate去开始生成必要的source文件

2.在Zynq_Design右击选择Create HDL Wrapper,这里Design Sources的顶层变成Zynq_Design_wrapper.v文件,现在设计准备去综合和实现,并且生成FPGA programming bitstream。

3.点击Generate Bitstream,当bitstream完成后,在弹出的对话框里选择Open Implemented Design,并点击OK。

Step 6:软件开发和在Zynq系统运行

现在我们准备将设计导入到Xilinx SDK,在SDK中,你将创建运行在zc702板上的软件(如果有)。HLS block的驱动产生在HLS导出到Vivado IP封装期间。该驱动程序必须在SDK里可以使用,以便于PS7软件可以与block进行交流。

1.在Vivado File菜单里选择Export > Export Hardware,并勾选Include Bitstream,然后在Vivado File菜单里选择Launch SDK。

2.在SDK File目录里选择New > Application Project,在project name里输入Zynq_Design_Test,点击next,选择Hello World,点击finish。在这里给zc702板通电并且测试HelloWorld应用,确保板子所有连接正确,在FPGA器件上去下载位流文件,并且可以看到zc702开发板上的文档。

3.选择Xilinx Tools > Program FPGA,此时注意到Done LED亮了,然后底部窗口点击SDK Terminal,选择Connection to Serial port,Port选择COM1,Baud Rate选择115200,点击OK

4.右击Zynq_Design_Test选择Run As > Launch on Hardware,最后在Terminal窗口验证Hello World是否被接受。

总结

本文介绍了如何使用Tcl脚本创建Vivado HLS IP,并且将HLS IP设计IP导入IP Integrator,以及如何将HLS IP 连接到使用AXI4-Lite接口和AXI4-Stream接口的Zynq AP SoC。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多