Northwest Logic PCI Express Gen3 IP核与S2C Virtex-7 ASIC原型验证平台实现协同验证 S2C以拥有业界最大的Prototype Ready™接口库为傲

俄勒冈州,比弗顿和加利福利亚州,圣何塞— 2014年8月18日– Northwest Logic和S2C Inc.今天联合发布信息称,Northwest Logic的PCI Express® (PCIe®) 3.0 解决方案,包含Expresso 3.0 IP核 (PCI Express 3.0 控制器IP核) 和全系列DMA核已在基于S2C的ASIC原型验证平台上验证完毕,而Northwest Logic的 PCI Express® (PCIe®) 3.0 解决方案全系列IP也被列入S2C ASIC验证平台最新支持的Prototype Ready™ IP名录。该验证方案在硬件上基于SERDES接口,8个通道,且每个通道数据传输速率高达8Gbps。此次Northwest Logic和S2C Inc.在联合验证方面的努力致力于增强用户在将高速PCIe IP核集成到用户自有SoC设计方面的信心,同时也能显著缩短用户项目实施周期。

“对于需要高速数据通信的系统而言,PCIe Gen3 是不可或缺的技术组成部分”,S2C首席执行官林俊雄先生表示,“ 与Northwest Logic在S2C Prototype Ready IP项目方面的合作,使用户可以立即获取到在高速大容量原型验证平台上经过验证的关键IP,而S2C的Prototype Ready IP项目目前已支持超过70多种经验证的IP核和子卡模组。参照经验证的IP性能和原型验证参考流程,IP集成工作将更易于实现,并缩短了用户的SoC设计周期。很高兴与Northwest Logic达成S2C Prototype Ready IP项目合作意向。”

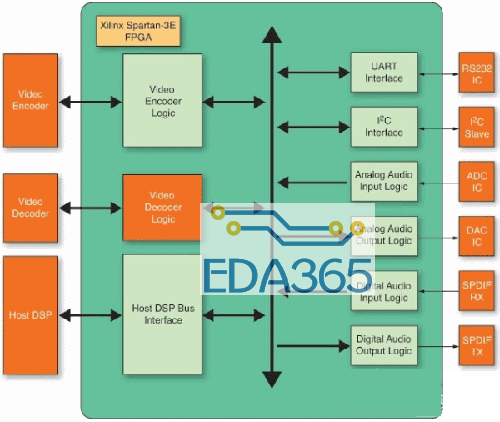

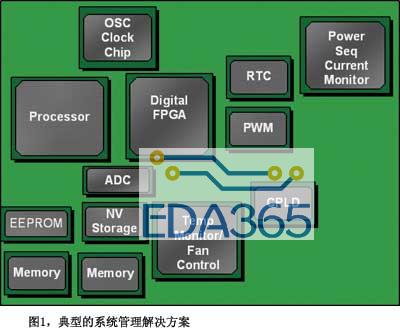

S2C特有的基于FPGA验证平台的解决方案使得工程师能够更快的实现和调试他们最新的对性能有超高要求的设计,同时也加速了系统级软件开发和细化更新工作。S2C TAI Logic Module系列FPGA验证平台为用户提供了高速的GTX接口,板级DDR3存储空间以及丰富的的接口模组,使用户能很容易的验证诸如PCIe, SATA以及USB等高性能接口IP。

Northwest Logic 提供了完整的 PCI Express 解决方案. 该解决方案包括 Northwest Logic针对PCI Express经硅验证的简单易用的高性能Expresso 3.0/2.1/1.1 核, 提供高性能scatter-gather DMA引擎的 DMA Back-End 核,驱动程序(针对Linux平台以及 Windows平台) 以及 应用软件。此外, Northwest Logic 也提供高性能的存储器控制器IP以及 MIPI 相关IP核.

“很高兴和S2C合作,” Northwest Logic总裁Brian Daellenbach说,”我们的客户能更快的完成他们的设计开发工作,而Northwest Logic高性能且功能完善的PCIe核与S2C现成的高品质原型验证平台的强强联合也使得客户更有信心“

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多