寄存器堆是构成微处理器的重要部件,缓存和传输操作数是它的基本作用,其性能优劣将直接影响处理器的处理能力。随着处理器并行处理能力的加强,寄存器堆的端口越来越多,端口的增加不但增加了功耗,也加大了读写延时,限制了处理器时钟频率的提高,成为高性能微处理器的片上存储瓶颈。

高速和低功耗是多端口寄存器堆的设计目标,但是两者之间相互约束。在Motorola的M.CORE处理器中,寄存器堆的功耗占整个芯片的16%,在数据通路中的比例更是高达42%。有研究表明,寄存器堆的功耗达到整个处理器芯片功耗的25%。因此,高速低功耗的多端口寄存器堆的设计成为未来存储器设计中极具挑战性的工作。

1 寄存器堆的功耗组成

1.1 寄存器堆的总体结构

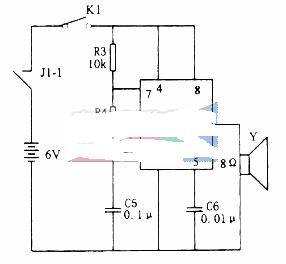

目前寄存器堆所采用的基本组成单元是6T SRAM。寄存器堆在电路结构上,可分为四个部分。第一是由存储单元构成的存储阵列;第二是由地址缓冲器、译码器、字线及其驱动器构成的地址路径;第三是由数据缓冲器、读写放大器、位线及其预充电路构成的数据路径;第四是读写控制逻辑。如图1所示。

1.2 多端口寄存器堆结构

多端口的存储单元一般每个端口都有自己的字线和位线,从而保证各个端口能够同时独立工作,以满足指令级并行的微处理器工作要求。但是这同时也导致了寄存器堆功耗的迅速提高。多端口读写位线一般有差分式和单端式两种,差分式读写以更高的数据准确性和读写速度应用于多数的多端口设计。其结构如图2所示。

1.3 多端口寄存器堆的功耗组成

1.3.1 基本单元SRAM

基本单元SRAM的功耗主要由三个部分组成。一是动态功耗,即电容充放电所消耗的功耗。二是短路功耗,即电源和地导通时所消耗的功耗。三是MOS管泄漏电流所引起的静态功耗。在三种功耗中动态功耗所占比重最大,而SRAM中位线连接许多存储体单元,其电容负载很大,位线充放电所引起的动态功耗就很大,占到总体动态功耗的80%,所以优化位线动态功耗对整个SRAM功耗降低影响很大。

1.3.2 电路组成部分

在多流水线结构的指令集并行微处理器中,一个时钟周期内可能对寄存器堆同时进行读写操作,假设每个操作的功耗是独立的,那么寄存器堆的总功耗即为每个操作所用功耗乘以单位时间内的操作次数。每个操作的功耗是电路各部分功耗的总和:译码逻辑功耗,存储阵列功耗,敏感放大器功耗,以及对敏感放大电路、预充电路和写驱动电路控制的驱动信号的功耗。因此,要降低寄存器堆的功耗,就应该同时从基本单元SRAM以及各个电路组成部分入手。

2 降低寄存器堆功耗的主要途径

2.1 降低电压摆幅

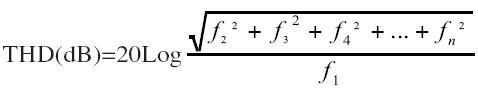

SRAM的动态功耗可由式(1)表示:

其中,α是活动因子,f是时钟频率,CL是负载电容,Vswing是信号摆幅,VDD是电源电压,位线动态功耗可以用式(2)表示:

f和Cbitload分别是位线的转换频率和电容负载,Vswing是位线电压摆幅,VDD是电源电压。由(2)式可以看出在转换频率和电源电压固定的条件下,可以通过减少位线电压摆幅来优化位线功耗,由于SRAM进行写操作时Vswing达到VDD,而读操作时Vswing很小,所以Vswing研究主要在写操作周期。

采用电荷分享方法的低位线摆幅(LVBS)低功耗SRAM结构设计可以降低位线电压幅值,如图3所示,当clk为0时,连接data_outO和data_outl的传输门关闭,无论data_in为何值,电荷分享驱动电路中两个MOS管中只有一个能被打开,所以输出data_out0和data_outl中只有一个输出为VDD,另一个输出则为GND。当clk为1时,两个MOS管同时关闭,异或非门输出为1,传输门打开。只要输出负载电容相等,根据电荷守恒定律,data_out0和data_out1的电压都变为VDD/2,即电压摆幅减少了50%,根据式(1)可知,位线动态功耗降低,从而达到降低寄存器堆功耗的目的。

APP下载

APP下载 登录

登录

热门文章

热门文章