莱迪思半导体公司近日发布了其LatticeSCTM系统芯片FPGA系列。该系列在高速应用中有着无以伦比的性能和连通性。 LatticeSC FPGA采用富士通的90纳米CMOS工艺技术并用300毫米硅片制造,能够加速芯片至芯片、芯片至存储器、高速串行、背板及网络数据通道的连通性,提供“超级性能”。与LatticeSC器件一起发布的还有莱迪思的第二代低成本的LatticeECP2系列,也是采用了相同的90 纳米工艺。

LatticeSC器件中集成了支持3.4Gbps数据率的高信道数的SERDES模块、提供业界的2Gbps 速度的PURESPEED 并行 I/O、创新的时钟管理结构、以500MHz频率工作的FPGA逻辑、密集的RAM块以及莱迪思特有的针对成本优化(MACO)的嵌入式结构化ASIC模块的掩膜式阵列。

“LatticeSC FPGA带来了业界所有可编程逻辑产品中的性能和强大的特性。LatticeSC系列与我们新的低成本 LatticeECP2器件、非易失MachXO 和LatticeXP器件一起,构建了市场上广阔、长的莱迪思FPGA产品线。”莱迪思公司市场副总裁Stan Kopec先生说道。“LatticeSC器件被设计成针对高性能基于协议的连通性的结构。” Kopec补充道。 “LatticeSC FPGA支持一大堆协议,包括PCI Express、 Serial RapidIO、Ethernet、 Fibre Channel、SONET/SDH、SPI4.2, 以及所有高性能存储器标准,包括DDR2、QDR2及RLDRAM。在一片FPGA 中,这样的创新、集成、对标准的支持以及速度都是空前的。” Kopec先生总结道。

LatticeSC: 高信道数的 SERDES + flexiPCS

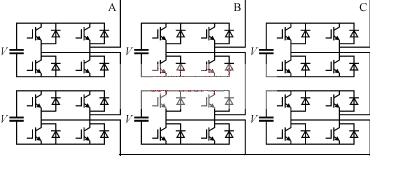

莱迪思FPSC(现场可编程系统芯片)是种将SERDES和嵌入式物理编码子层(PCS)模块集成在一片FPGA上的可编程逻辑器件。 LatticeSC器件引领了新概念:高达32个 SERDES信道、每个信道的数据率从600Mbps至3.4Gbps。为了支持驱动长度达到60英寸的背板应用,设计者可以使用SERDES内置的发送预加重及接收均衡特性。

LatticeSC SERDES还具有极低的典型功耗:在 3.125Gbps的速率下,100mw/信道。抖动指标:总发送抖动在3.2Gbps速率下为0.29 UI,总接收抖动容限是0.8UI。此外, LatticeSC器件还具备其它的一些可编程特性,诸如AC/DC耦合以及半速模式,能在用户实现设计的过程中为其提供非凡的灵活性。

FlexiPCS 模块可以经过配置来支持一系列流行的数据协议,包括PCI-Express、1.02 或 者 2.04 Gbps Fibre Channel、 Gigabit Ethernet (1000 BaseX)、10 Gigabit Ethernet (XAUI)、Serial RapidIO及 SONET (STS-12/STS-12c、STS-48/STS-48c和 TFI-5,支持10Gbps及以上速率)。FlexiPCS模块具有的Ethernet和 PCI Express支持,拥有嵌入式的编解码物理层功能、时钟容限补偿、CRC发生/校验及多信道对齐功能。

莱迪思的创新:低成本优化(MACO)的掩膜阵列

虽然结构化的ASIC缺乏FPGA的灵活性,但由于其密度和性能,它们变得越来越流行。与全定制或者标准单元的ASIC不同,结构化的ASIC设计成本要低得多,因为它们只将一小部分掩膜用作定制。莱迪思在每一片LatticeSC FPGA中嵌入了多达12个结构化的ASIC模块,称为MACO模块。每个MACO模块大约有5万个ASIC门可用来实现需要性能、硅片面积和功耗的知识产权(IP)核。MACO模块还提供充足的至I/O引脚的布线连结、RAM块及可编程逻辑块。

莱迪思计划推出一系列LatticeSC器件,它们拥有预制的、覆盖许多要求高速连结的常见应用的模块。预制的、基于MACO的IP将包含莱迪思创新的flexiMAC 多协议通信引擎,它支持多层协议,诸如PCI Express、Ethernet、以及 SPI4.2 和高速 DRAM/SRAM 存储控制器。莱迪思将把这些标准MACO IP功能预先编程到其LatticeSC系列的特别版本中,称为M -系列。

LatticeSC PURESPEED I/O: 2Gbps 超级性能和连通性

LatticeSC PURESPEED I/O 支持许多差分和单端I/O标准,包括LVTTL、LVCMOS、SSTL、HSTL、GTL+、LVDS、LVPECL和Hypertransport。每个LatticeSC I/O引脚含有一个输入延时(INDEL)对齐模块,该模块有间隔为40ps的144个抽头。对于高速源同步I/O, PURESPEED I/O技术所特有的适应输入逻辑(AIL)模块能够对闭环引脚进行时序监控。该特性能够一位一位地动态地保持恰当的建立和保持时间裕量。采用这一特性,能够使设计在单个引脚上地支持高达2Gbps的速度。

LatticeSC FPGA还提供用于SDR、DDR1和DDR2接口的专用的变速箱逻辑。片上的时钟分频器支持变速箱逻辑的时钟要求,从而无需在此情况下使用通用的PLL/DLL资源。

LatticeSC FPGA提供低功耗的内部终端电阻(ODT),能够减小残存信号的长度,从而提高性能。器件上终端电阻的动态切换是自动完成的,支持诸如DDR2存储器等的标准。

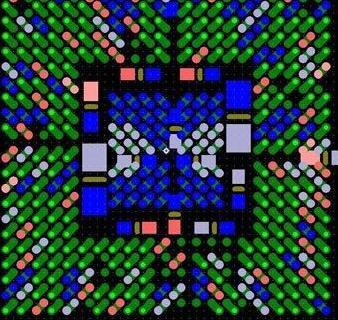

FPGA结构和嵌入式块RAM

LatticeSC 器件采用富士通的90纳米COMS工艺技术,结合经过优化的逻辑块和丰富的布线资源,制造出的FPGA结构可轻易地以达到500MHz的频率工作(例如: 64位地址解码)。其阵列的基本逻辑元素是可编程功能单元(PFU),可以配置成逻辑、算术和分布式RAM/ROM功能。PFU分成四个片段,每个片段含有两个4输入的SRAM查找表(LUT),外加寄存器。这些片段可以独立配置并且能够串联,这样PFU就能完成更大的功能了。该系列的密度范围从15K到 115K个 LUT。

LatticeSC器件提供1至7.8兆位的能够以500MHz频率工作的嵌入式RAM块(EBR)。每个 18Kb的 sysMEM EBR块可以实现单口、双口、伪双口或者FIFO存储器。专用的FIFO支持逻辑使得LatticeSC器件能够有效地实现 FIFO而无需耗费LUT或布线资源来产生标志位。

LatticeSC FPGA还集成了具有层次结构的时钟资源。与其它器件不同,LatticeSC FPGA既有PLL又有DLL资源,为时钟管理问题提供了“无折衷”的解决方案。

针对低功耗应用的1V核电源

LatticeSC FPGA结构具有业界的、拓展了工作范围的电源核,支持1.2V及1V的核Vcc电源。功耗要求很高的用户可以采用1V电源,从而将FPGA电源的功耗降低50%,与此同时,其性能仅仅降低了15%。

FreedomChip成本削减

对于大批量的应用,莱迪思还宣布了针对其LatticeSC系列的成本削减方法的计划。通过把选定的LatticeSC FPGA设计转换到引脚兼容的 Lattice FreedomChip,客户能够将其价格降低50%。通过自动插入扫描逻辑,能用客户的网表来制造低成本的经过测试的定制芯片,而不需要与传统的结构化ASIC相伴的艰难的后端设计转换。

LatticeSC FPGA的应用实例

LatticeSC FPGA 的一个典型的应用是在一个多重服务网络系统中的通用连通桥。单片LatticeSC器件能够支持当今网络中使用的多种数据流。为了进行流量整形, LatticeSC器件利用嵌入在结构化ASIC模块中的多个SPI4.2核,无缝地实现与多个10G网络处理器的接口。要缓冲这些更快的线速,需要高速存储器接口。LatticeSC支持所有的存储器标准。为了与兆兆位的交换结构接口,LatticeSC FPGA多能够以32个SERDES信道来驱动系统背板,并且支持许多串行标准,如Serial RapidIO、SONET/SDH、PCI Express、Ethernet以及 Fibre Channel。

设计工具及IP支持

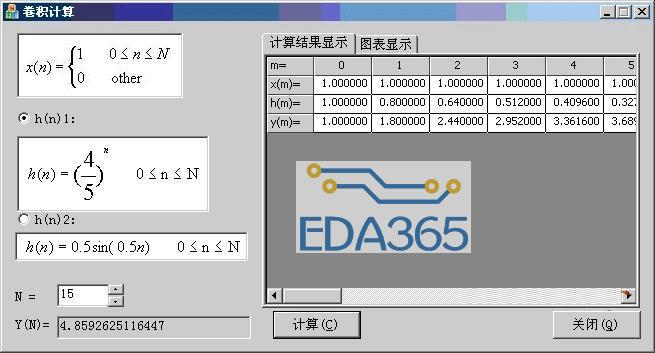

ispLEVER® 5.1版 Service Pack 2设计工具套件提供对LatticeSC器件的设计支持。ispLEVER工具能让设计者在同一个软件包中使用所有莱迪思的数字器件,并且包含来自 Mentor Graphics和Synplicity的仿真及综合工具。

莱迪思及其IP伙伴将提供大量的IP核,它们特别适用于大批量的应用。

价格及获取

LFSC25以600Mbps至 3.4Gbps的速率工作,拥有8或16个SERDES信道,取决于封装选择。其FPGA结构具有25000个PFU,1.92兆位的嵌入式RAM块,以及6个MACO结构化的ASIC模块。LFSC25有900引脚的fpBGA和1020引脚的flip chip BGA两种封装形式。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多