本系列文章的第一部分介绍了关于锁相环(PLL)的基本概念,说明了PLL架构和工作原理,同时以一个例子说明了PLL在通信系统中的用途。

在第二部分中,我们将侧重于详细考察与PLL相关的两个关键技术规格:相位噪声和参考杂散。导致相位噪声和参考杂散的原因是什么,如何将其影响降至最低?讨论将涉及测量技术以及这些误差对系统性能的影响。我们还将考虑输出漏电流,举例说明其在开环调制方案中的重要意义。

振荡器系统中的噪声

在任何振荡器设计中,频率稳定性都至关重要。我们需要考虑长期和短期稳定性。长期频率稳定性是关于输出信号在较长时间(几小时、几天或几个月)内的变化情况。其通常以一定时间内的比率Δf/f来规定,单位为百分比或dB。

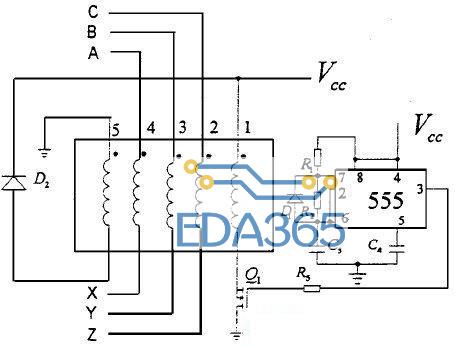

短期稳定性则是关于几秒或更短时间内的变化情况。这些变化可能是随机的,也可能是周期性的。可以使用频谱分析仪来检查信号的短期稳定性。图1显示了一种典型频谱,其中随机和离散频率成分导致出现大范围的波裙和杂散波峰。

图1.振荡器的短期稳定性。

信号源中的已知时钟频率、电力线干扰和混频器产品都可能引起离散杂散成分。随机噪声波动引起的扩张是相位噪声造成的。其可能是有源和无源器件中的热噪声、散粒噪声和/或闪烁噪声造成的。

电压控制振荡器中的相位噪声

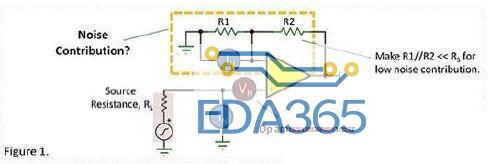

在考察PLL系统中的相位噪声之前,我们先看看电压控制振荡器(VCO)中的相位噪声。理想的VCO应该没有相位噪声。在频谱分析仪上看到的输出应是一条谱线。当然,事实并非如此。输出上会有抖动,频谱分析仪会显示出相位噪声。为了便于理解相位噪声,请考虑一种相量表示方式,如图2所示。

图2.相位噪声的相量表示。

图中所示信号的角速度为wO,峰值幅度为VSPK。叠加于其上的误差信号的角速度为wm。Δqrms表示相位波动的均方根值,单位为rms度数。

在许多无线电系统中,必须符合总积分相位误差规格的要求。该总相位误差由PLL相位误差、调制器相位误差和基带元件导致的相位误差构成。例如,在GSM中,允许的总相位误差为5度rms。

Leeson方程

Leeson(第6项参考文献)提出了一项方程,用以描写VCO中的不同噪声组分。

其中:

LPM为单边带相位噪声密度(dBc/Hz)

F为工作功率水平A(线性)下的器件噪声系数

k为玻尔兹曼常数,1.38×10–23J/K

T为温度(K)

A为振荡器输出功率(W)

QL为加载的Q(无量纲)

fO为振荡器载波频率

fm为载波频率失调

要使Leeson方程有效,以下条件必须成立:

•fm,载波频率失调大于1/f闪烁角频;

•已知工作功率水平下的噪声系数;

•器件运行呈线性特征;

•Q包括元件损耗、器件加载和缓冲器加载的影响;

•振荡器中只使用了一个谐振器。

图3.VCO中的相位噪声与频率失调的关系。

Leeson方程只适用于断点(f1)与从“1/f”(更普遍的情况是1/fg)闪烁噪声频率到超过后放大白噪声将占据主导的频率点(f2)的跃迁之间的膝部区域。如图3所示[g=3]。f1应尽量低;一般地,它小于1kHz,而f2则在几MHz以内。高性能振荡器要求使用针对低1/f跃迁频率而专门选择的器件。有关如何尽量降低VCO中相位噪声的一些指导方针如下:

1.使变容二极管的电压足够高(一般在3至3.8V)

2.在直流电压电源上用滤波。

3.使电感Q尽量高。典型的现成线圈的Q在50至60之间。

4.选择一个噪声系数最小且闪烁频率低的有源器件。闪烁噪声可借助反馈元件降低。

5.多数有源器件都展现出较宽的U形噪声系数与偏置电流之关系曲线。用该信息来为器件选择最佳工作偏置电流。

6.使振荡电路输出端的平均功率最大化。

7.在对VCO进行缓冲时,要使用噪声系数最低的器件。

闭环

前面,我们讨论了自由运行VCO中的相位噪声,考虑了降低该噪声的方式,接下来,我们将考虑闭环(见本系列第一部分)对相位噪声的影响。

图4所示为PLL中的主要相位噪声贡献因素。系统传递函数可通过以下等式来描述:

ClosedLoopGain=

G=

ClosedLoopGain=

APP下载

APP下载 登录

登录

热门文章

热门文章