O 引言

电路中的功率消耗源主要有以下几种:由逻辑转换引起的逻辑门对负载电容充、放电引起的功率消耗;由逻辑门中瞬时短路电流引起的功率消耗;由器件的漏电流引起的消耗,并且每引进一次新的制造技术会导致漏电流20倍的增加,漏电流引起的消耗已经成为功率消耗的主要因素。目前降低功耗的方法主要有:减小电源电压、调整晶体管尺寸、采用并行和流水线的系统结构、利用睡眠模式、采用绝热逻辑电路等。其中,能量回收逻辑就是基于绝热计算发展起来的一种低功耗设计技术。

这里简单介绍一种使用单相正弦电源时钟的能量回收逻辑,并用这种原理电路设计了一个两位的数字乘法器电路,与静态CMOS数字乘法器相比,这种能量回收乘法器能够大大降低功率消耗。

1 单相正弦电源时钟能量回收逻辑电路工作原理

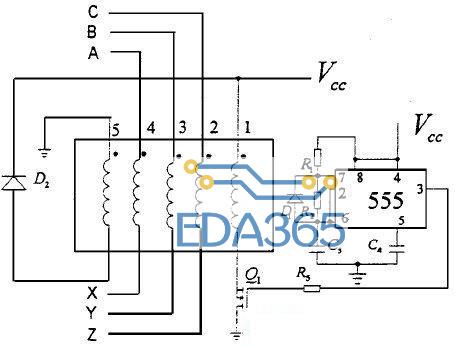

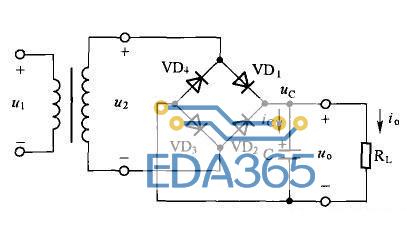

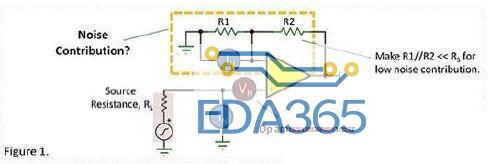

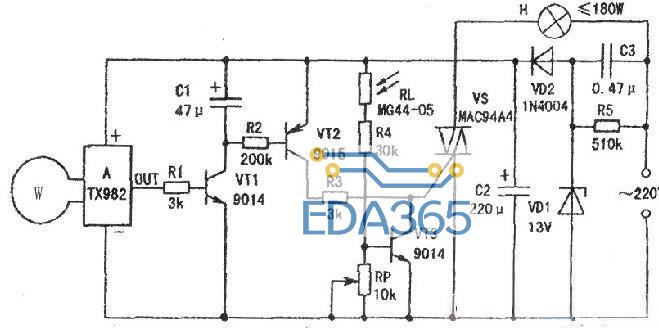

以反相器为例说明这种电路的工作原理,如图1所示。M1和M2的连接方式与传统的静态CMOS逻辑电路相似。不同的是电源不再是恒定不变的,而是用一个正弦信号代替,这个信号同时起到同步电路工作的作用,因此又称作电源时钟。M3和M4连接成二极管的形式用来控制充放电的路径。

当输入信号B为逻辑“O”时,M1导通,M2截止。正弦信号正半周时,通过M3和M1向负载电容充电,一旦电容充电到最大值,M3能够阻止电容向输入正弦时钟信号放电,输出保持在高电平不变。当输入信号B为逻辑“1”时,M1截止,M2导通。正弦信号负半周时,负载电容通过M2和M4向输入正弦时钟信号放电,一旦电容放电到最小值,M4能够阻止输入正弦时钟信号向电容充电,输出保持为低电平不变。

2 基于单相能量回收电路的乘法器电路设计

2.1 基于单相能量回收电路的乘法器

两位乘法器能够实现2位二进制数的乘法运算,设A1A0,B1B0为乘数和被乘数,P3P2P1P0为乘法运算得到的积,由卡诺图(见图2)得到两位乘法器的输出逻辑函数表达式分别为:

APP下载

APP下载 登录

登录

热门文章

热门文章