1.1S3C2440系统中断

CPU和外设构成了计算机系统,CPU和外设之间通过总线进行连接,用于数据通信和控制,CPU管理监视计算机系统中所有硬件,通常以两种方式来对硬件进行管理监视:l查询方式:CPU不停的去查询每一个硬件的当前状态,根据硬件的状态决定处理与否。好比是工厂里的检查员,不停的检查各个岗位工作状态,发现情况及时处理。这种方式实现起来简单,通常用在只有少量外设硬件的系统中,如果一个计算机系统中有很多硬件,这种方式无疑是耗时,低效的,同时还大量占用CPU资源,并且对多任务系统反应迟钝。

l中断方式:当某个硬件产生需要CPU处理的事件时,主动通过一根信号线“告知”CPU,同时设置某个寄存器里对应的位,CPU一旦发现这根信号线上的电平有变化,就会中断当前程序,然后去处理发出该中断请求。这就像是医院重危病房,病房每张病床床头有一个应急按钮,该按钮连接到病房监控室里控制台一盏指示灯,只要该张病床出现紧急情况病人按下按钮,病房监控室里电铃会响起,通知医护人员有紧急情况,医护人员这时查看控制台上的指示灯,找出具体病房,病床号,直接过去处理紧急情况。中断处理方式相对查询方式要复杂的多,并且需要硬件的支持,但是它处理的实时性更高,嵌入式系统里基本上都使用这种方式来处理。

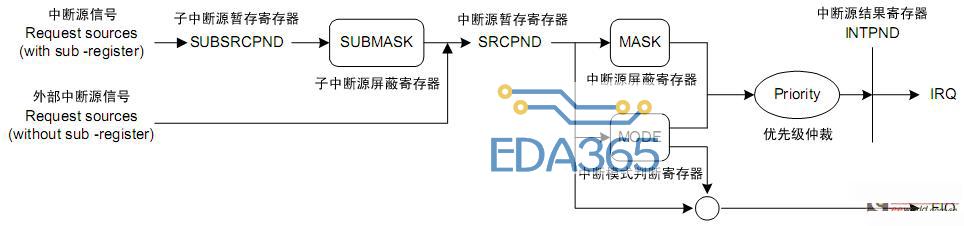

系统中断是嵌入式硬件实时地处理内部或外部事件的一种机制。对于不同CPU而言,中断的处理只是细节不同,大体处理流程都一样,S3C2440A的中断控制器结构如下图所示:

图3-3S3C2440中断控制器

中断请求由硬件产生,根据中断源类型分别将中断信号送到SUBSRCPND(SubSourcePending)和SRCPND(SourcePending)寄存器,SUBSRCPND是子中断源暂存寄存器,用来保存子中断源信号,SRCPND是中断源暂存寄存器,用来保存中断源信号。中断信号可通过编程方式屏蔽掉,SUBMASK是子中断源屏蔽寄存器,可以屏蔽指定的子中断信号,MASK功能同SUBMASK用来屏蔽中断源信号。中断分为两种模式:一般中断的和快速中断,MODE是中断模式判断寄存器,用来判断当前中断是否为快速中断,如果为快速中断直接将快速中断信号送给ARM内核,如果不是快速中断,还要将中断信号进行仲裁选择。S3C2440A支持多达60种中断,很有可能多个硬件同时产生中断请求,这时要求中断控制器做出裁决,Priority是中断源优先级仲裁选择器,当多个中断产生时,选择出优先级最高的中断源进行处理,INTPND是中断源结果寄存器,里面存放优先级仲裁出的唯一中断源。

1中断的产生-中断源

S3C2440A支持60种中断源,基本上满足了开发板内部,外部设备等对中断的需求。其中每一个中断源对应寄存器中的一位,显然要支持60种中断至少需要二个32位寄存器,SUBSRCPND和SRCPND分别保存中断源信号。S3C2440A对60种中断源的管理是按层级分的。如图3-4所示:

图3-4中断源信号复合示意图

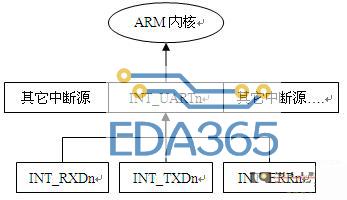

S3C2440A将中断源分为两级:中断源和子中断源,中断源里包含单一中断源和复合中断源,复合中断源是子中断源的复合信号。如实时时钟中断,该硬件只会产生一种中断,它是单一中断源,直接将其中断信号线连接到中断源寄存器上。对于复合中断源,以UART串口为例进行说明,S3C2440A可以支持3个UART串口,每个串口对应一个复合中断源信号INT_UARTn,每个串口可以产生三种中断,也就是三个子中断:接收数据中断INT_RXDn,发送数据中断INT_TXDn,数据错误中断INT_ERRn,这三个子中断信号在中断源寄存器复合为一个中断信号,三种中断任何一个产生都会将中断信号传递给对应的中断源INT_UARTn,然后通过中断信号线传递给ARM内核。

图3-5UART串口中断源信号复合示意图

总中断源详下面表中列出了S3C2440A部分中断源,它分别对应中断源寄存器里某个位:详细中断源请查看S3C2440A硬件手册。

表3-5部分中断源信号

| 中断源 | 描述 | 优先级仲裁分组 |

| INT_ADC | 数模转换和触摸屏中断 | ARB5 |

| INT_RTC | 实时时钟中断 | ARB5 |

| INT_UART0 | UART0中断(包含子中断) | ARB5 |

| INT_NFCON | NandFlash控制中断 | ARB4 |

| INT_WDT_AC97 | 看门狗中断 | ARB1 |

| EINT8-23 | 外部中断8~23(包含外部子中断) | ARB1 |

| EINT4-7 | 外部中断4~7(包含外部子中断) | ARB1 |

| EINT3 | 外部中断3 | ARB0 |

| EINT2 | 外部中断2 | ARB0 |

| EINT1 | 外部中断1 | ARB0 |

| EINT 0 | 外部中断0 | ARB0 |

中断信号除上述分法之外,还可以按照硬件位置分为:外部中断源和内部中断源。

l内部中断源:它是嵌入式系统中常见硬件产生的中断信号,比如:UART串口中断源,时钟Timer中断源,看门狗中断源等

l外部中断源:有时嵌入式系统里要在外部接口上挂载一些外部设备,这些设备并不是一个通用嵌入式系统里必备硬件,比如:蓝牙模块,各种传感器,WIFI无线通信模块,这些硬件也要产生中断让CPU来处理数据,因此这些外设硬件通过中断信号线连接到中断控制器上,它们产生的中断叫做外部中断信号。它们有着和内部中断一样的处理机制,只不过,它没有一个固定的中断号与之对应,硬件与嵌入式系统的连接方式与中断处理完全由系统硬件与软件设计者实现。

外设硬件通过输入输出接口I/O Ports挂接到嵌入式系统上,I/O Ports向外设提供外部中断信号线,输出电源,频率时钟和输入输出信号线,外部硬件根据自己需要连接到I/O Ports上,产生中断时向外部中断信号线上送出中断信号,通过外部中断信号线传递到中断控制器。

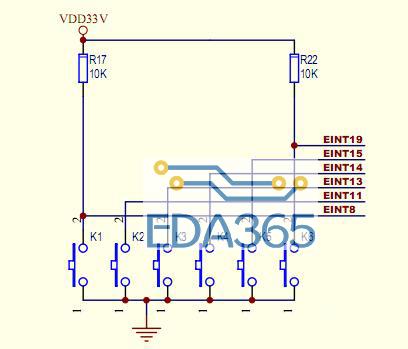

按键Key可以认为最为简单的一种硬件设备了,如下图所示:

图3-6按键硬件接线原理图

它功能很简单,可以将电路接通,按键K1~K6一端接地为低电平,另外一端接电源正极为高电平,EINT8,EINT11,EINT13,EINT14,EINT15,EINT19六根中断信号线分别和高电平端按键相连,当按键按下时电路接通,整个电路变成低电平,中断信号线上电压产生变化,通过设置中断触发方式,产生外部中断请求,输入到CPU内部,从而实现按键中断控制。

S3C2440A可以支持EINT0~EINT23共24种外部中断,完全可以满足小型嵌入式设备外设硬件的需求。

外部中断源也分为外部中断源和外部子中断源,其处理方式和内部中断源基本一样。

1.1.1中断优先级

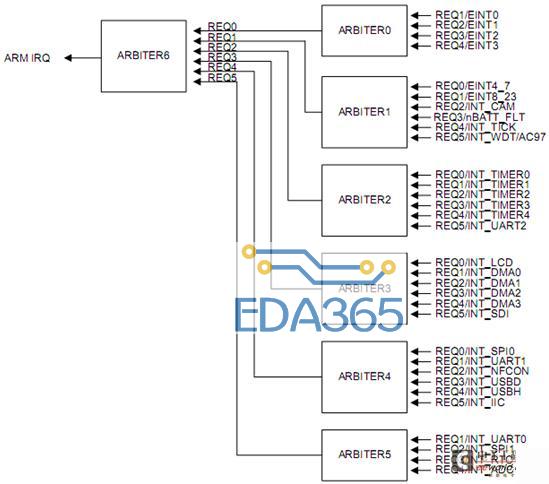

S3C2440A支持60种中断,多个硬件可能同时产生中断请求,由于CPU只能处理一个中断,中断控制器怎么选择出一个最佳的中断,交给ARM内核进行处理呢?中断控制器采用优先级仲裁比较的方式进行选择,找出优先级最高的中断源。中断控制器将60种中断源分成7组,如下图所示,它类似体育赛事里的比赛方式,所有参赛选手在小组赛PK,选择出小组赛最优秀选手,然后进入决赛阶段和其它小组最优先选择再PK,最后优胜者就是总冠军。其中ARBITER0~ARBITER5为“小组赛”阶段,中断源信号在各自小组里进行优先级仲裁,选择出最高优先级中断信号,每小组选出的中断信号送到ARBITER6,也就是决赛阶段,选择出最高优先级中断信号,交给ARM内核。

图3-7S3C2440优先级仲裁示意图

中断信号在7个分组里PK时的优先级是可编程的,通过PRIORITY寄存器进行优先级设置。如下表(只列出PRIORITY寄存器部分位):

表3-6中断优先级控制寄存器(PRIORITY)

| 寄存器名 | 地址 | 是否读写 | 描述 | 复位默认值 |

| PRIORITY | 0x4A00000C | R/W | 中断优先级控制寄存器 | 0x7F |

| PRIORITY | 位 | 描述 | 初始值 |

| ARB_SEL6 | [20:19] | 仲裁组6优先级排序方式 00 = REQ 0-1-2-3-4-5 01 = REQ 0-2-3-4-1-5 10 = REQ 0-3-4-1-2-5 11 = REQ 0-4-1-2-3-5 | 0x00 |

| ARB_SEL5 | [18:17] | 仲裁组5优先级排序 00 = REQ 1-2-3-4 01 = REQ 2-3-4-1 10 = REQ 3-4-1-2 11 = REQ 4-1-2-3 | 00 |

| … | … | … | … |

| ARB_MODE6 | [6] | 仲裁组6优先级是否轮转: 0 =不轮转,1 =轮转 | 1 |

| ARB_MODE5 | [5] | 仲裁组5优先级是否轮转: 0 =不轮转,1 =轮转 | 1 |

| … | … | … | … |

通过设置仲裁组n优先级排序方式位,设置每个仲裁组内中断信号的优先级顺序,比如:ARB_SEL5分组时包含四个中断信号:REQ1 INT_UART0, REQ2 INT_SPI1, REQ3 INT_RTC, REQ4 INT_ADC,ARB_SEL5位采用默认值:00,当INT_UART0和INT_RTC中断信号同时产生时,INT_UART0会被选出,通过可编程方式改变优先级排序方式来改变中断信号优先级。

ARB_MODE0~ ARB_MODE6为每个仲裁分组的优先级轮转设置位,采用默认值时,当前中断信号被选择处理之后,再次产生中断请求时,它的优先级自动轮转到该组最低,这样可以保证优先级低的中断信号可以被及时处理,不至于出现优先级高且中断请求频繁的中断每次都被优先处理,而优先级低的被“饿死”的情况。显然,这种方式更民主,实时性更佳。

2中断控制器相关寄存器

(1)SUBSRCPND子中断源暂存寄存器表3-7子中断源暂存寄存器(SUBSRCPND)

| 寄存器名 | 地址 | 是否读写 | 描述 | 复位默认值 |

| SUBSRCPND | 0x4A000018 | R/W | 子中断源暂存寄存器,保存中断请求状态: 0:没有中断请求信号 1:中断请求信号产生 | 0x00000000 |

| SUBSRCPND | 对应SRCPND | 位 | 描述 | 初始值 |

| Reserved | 无 | [31:15] | 未使用 | 0 |

| INT_AC97 | INT_WDT_AC97 | [14] | 0 =未产生中断1 =产生中断 | 0 |

| … | … | … | … | … |

| INT_RXD0 | INT_UART0 | [0] | 0 =未产生中断1 =产生中断 | 0 |

该寄存器用来标识保存子中断源信号,当某个子中断信号产生之后,SUBSRCPND对应位被自动置1,该位会一直保持被置位,只到中断处理程序将其清除为止,需要注意一下,清除中断是通过向对应位写入1来清除,而不是写入0,写入0无效。

(2)INTSUBMSK子中断源屏蔽寄存器

表3-8子中断源屏蔽寄存器(INTSUBMSK)

| 寄存器名 | 地址 | 是否读写 | 描述 | 复位默认值 |

| INTSUBMSK | 0x4A00001C | R/W | 子中断源信号屏蔽存寄存器,设置相应位来屏蔽中断信号: 0:未屏蔽,中断可用 1:屏蔽中断信号 | 0xFFFF |

| INTSUBMSK | 位 | 描述 | 初始值 |

| Reserved | [31:15] | 未使用 | 0 |

| INT_AC97 | [14] | 0 =未屏蔽1 =屏蔽中断 | 1 |

| … | … | … | … |

| INT_RXD0 | [0] | 0 =未屏蔽1 =屏蔽中断 | 1 |

该寄存器用来屏蔽子中断源信号,默认值为全部子中断都被屏蔽掉,因此要想处理某个硬件中断,必须要打开中断屏蔽位,通过写入0来取消屏蔽中断。

(3)SRCPND中断源暂存寄存器

表3-9中断源暂存寄存器(SRCPND)

| 寄存器名 | 地址 | 是否读写 | 描述 | 复位默认值 |

| SRCPND | 0x4A000000 | R/W | 中断源暂存寄存器,保存中断请求状态: 0:没有中断请求信号 1:中断请求信号产生 | 0x00000000 |

| SRCPND | 位 | 描述 | 初始值 |

| INT_ADC | [31] | 0 =未产生中断1 =产生中断 | 0 |

| … | … | … | … |

| EINT0 | [0] | 0 =未产生中断1 =产生中断 | 0 |

该寄存器用来保存中断源信号,当某个中断信号产生之后,SRCPND对应位被自动置1,该位会一直保持被置位,只到中断处理程序将其清除为止,需要注意一下,清除中断是通过向对应位写入1来清除,而不是写入0,写入0无效。

(4)INTMSK中断源屏蔽寄存器

表3-10中断源屏蔽寄存器(INTMSK)

| 寄存器名 | 地址 | 是否读写 | 描述 | 复位默认值 |

| INTMSK | 0x4A000008 | R/W | 中断源信号屏蔽存寄存器,设置相应位来屏蔽中断信号: 0:未屏蔽,中断可用 1:屏蔽中断信号 | 0xFFFFFFFF |

| INTMSK | 位 | 描述 | 初始值 |

| INT_ADC | [31] | 0 =未屏蔽1 =屏蔽中断 | 1 |

| … | … | … | … |

| EINT0 | [0] | 0 =未屏蔽1 =屏蔽中断 | 1 |

该寄存器用来屏蔽中断源信号,默认值为全部中断都被屏蔽掉,因此要想处理某个硬件中断,必须要打开中断屏蔽位,通过写入0来取消屏蔽中断。

(5)INTPND最高优先级中断暂存寄存器

表3-11最高优先级中断暂存寄存器(INTPND)

| 寄存器名 | 地址 | 是否读写 | 描述 | 复位默认值 |

| INTPND | 0x4A000010 | R/W | 最高优先级中断暂存寄存器里面保存有经过优先级仲裁的结果: 0:没有中断请求信号 1:中断请求信号产生 | 0x00000000 |

| INTPND | 位 | 描述 | 初始值 |

| INT_ADC | [31] | 0 =未产生中断1 =产生中断 | 0 |

| … | … | … | … |

| EINT0 | [0] | 0 =未产生中断1 =产生中断 | 0 |

该寄存器保存了经过优先级仲裁出的中断信号位,它是所有当前中断请求里优先级别最高的中断,因此该寄存器里的值最多有一位被置1,通常中断处理程序中会通过读取该寄存器的值来获得当前正在处理的中断请求。中断处理完成之后,通过写入1来清除中断。

(6)INTOFFSET中断号偏移量寄存器

表3-12中断号偏移量寄存器(INTOFFSET)

| 寄存器名 | 地址 | 是否读写 | 描述 | 复位默认值 |

| INTOFFSET | 0x4A000014 | R | 中断号偏移量寄存器,用来保存当前处理的中断号 | 0x0000000 |

该寄存器里存放的是经过优先级仲裁出的中断信号对应的中断号,是一个0~31之间的整数,其实它就是INTPND里对应的位号,比如:INT_UART0产生了中断,INTPND里第28位置1,INTOFFSET里保存的整数就是28,多出来这个寄存器的目的主要是方便中断处理程序查询中断源,清除中断源:

#define TIMER0_IRQ_OFT10//时钟0定时中断

#define EINT0_IRQ_OFT0//开发板K1按键1对应外部中断EINT0

voidhandle_irq()

{

unsigned long irqOffSet = INTOFFSET;//取得中断号

switch(irqOffSet)

{

case TIMER0_IRQ_OFT://当前中断为定时器0中断

do_timer();//跳入定时器0处理程序

break;

case EINT0_IRQ_OFT://当前中断为K1按键触发

do_key1_pressed();//处理K1按下事件

break;

}

SRCPND &= (1<

}

(7)INTMOD中断模式寄存器

表3-13中断模式寄存器(INTMOD)

| 寄存器名 | 地址 | 是否读写 | 描述 | 复位默认值 |

| INTMOD | 0x4A000004 | R/W | 中断模式寄存器,指定对应中断模式: 0 = IRQ一般中断模式 1 = FIQ快速中断模式 | 0x0000000 |

| INTMOD | 位 | 描述 | 初始值 |

| INT_ADC | [31] | 0 = IRQ 1 = FIQ | 0 |

| … | … | … | … |

| EINT0 | [0] | 0 = IRQ 1 = FIQ | 0 |

通过设置ARM内核产生中断。需要注意的是,快速中断不存在优先级仲裁,只能有一位被设置为FIQ模式。

APP下载

APP下载 登录

登录

热门文章

热门文章