采用电路仿真ADS软件进行了原理图及版图仿真,研究了增益控制电路在放大器中的位置对性能的影响。最终实现了在6~9GHz频率范围内,1 dB压缩点输出功率大于33 dBm,当控制电压在-1~0 V之间变化时,放大器的增益在5~40dB之间变化,增益控制范围达到了35 dB.将功率放大器与增益控制电路制作在同一个单片集成电路上,面积仅为3.5 mm×2.3 mm,具有灵活易用、集成度高和成本低的特点,可广泛应用于卫星通信和数字微波通信等领域。

甚小口径终端(verysmall aperture terminal,VSAT)和数字微波通信(也称P2P通信)系统为商用微波无线信息传输系统,具有覆盖范围大、集成化程度高、对所有地点提供相同的业务种类和服容性好、扩容成本低、所需时间短、通信质量好和安装方便的特点。

功率放大器是微波无线信息传输系统的核心元器件,其性能直接影响发射机的作用半径、线性特性以及整个系统的效率,它通常是系统中成本最高的元器件。当代微波无线信息传输系统小型化的趋势越来越明显,这就要求元器件的集成度越来越高。

国外开展商用单片功率放大器研究较早,其中日本Eudyna公司的产品性能较佳,占领的市场份额最大,美国Hittite公司和Triquint公司也在近两年推出了相应的产品。中国在GaAs材料生长和器件研制方面也积极开展了相关的研究工作。

由于该功率放大器应用于商用领域,所以对其性能和成本都有较高的要求,本文通过电路设计,将常规功率放大器的功能进行扩展,增加增益控制功能,能够在实现系统小型化的同时,降低成本,同时,不会影响功率放大器的输出功率和效率等相关指标。

本文研制的多功能功率放大器单片集成电路的面积与同样指标的功率放大器面积一样,约为8 mm2,传统室外单元的电压控制可变衰减器(voltage variable attenuator,VVA)的面积约为1.7 mm2,可见文中的多功能功率放大器将芯片面积节省了17.5%,有利于系统的小型化和成本的降低。

1 增益控制电路的设计原理

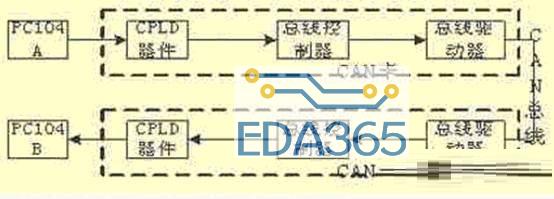

增益控制电路的作用是通过改变控制电压,达到改变放大器增益的目的。增益控制电路在放大器中的位置至关重要,若放置于放大器的末级,会由于自身的损耗而影响输出功率,放置于中间,会使放大器的中间级因无法将末级推饱和,从而影响效率。通过以上分析,将增益控制电路放置于放大器的第一级。

增益控制电路的原理如图1所示,由两个场效应晶体管(field effect transistor,FET)组成,FET1的漏极与FET2的源极连接在一起,射频信号从FET1的栅极输入,从FET2的漏极输出。图1中:Vc为控制电压;Vgs为栅压;Vdd为漏压;V1表示两个FET连接点的电压;Ids为FET1和FET2的漏极到源极的电流,图1中FET1的源极和FET2的漏极连接于同一节点,所以Ids同时流经FET1和FET2.该电路通过改变Vc的电压值来改变增益。

图1 增益控制电路拓扑图

FET工作在饱和区时的跨导gm,Ids与Vgs的关系如图2所示。FET1的栅压Vgs保持不变,则源漏电阻值的变化不会很大,在工作点的阻抗约为10Ω,由欧姆定律可知,V1的电压值由Ids决定。FET2的漏压Vds保持不变,Vc变化时,FET2的栅压相应变化,由图2的曲线可以看出,当栅压变化时,gm会产生变化,FET2的放大倍数则相应改变。同时,FET2的栅压变化时,根据图3,Ids会有较大的变化。根据之前的分析,Ids变化时,V1的值也会相应产生较大的变化,当V1小于1V时,FET1工作在图3中的线性区,增益受漏压影响较大,所以当V1变化时,FET1的放大倍数也会相应变化。这样,FET1和FET2的增益都受Vc的控制,其共同的增益变化量成为功率放大器的增益变化范围。

图2 gm,Ids与Vgs的关系曲线

图3 Vds,Vgs与Ids的关系曲线

2 功率放大器的设计原理

本文选用中国电子科技集团公司第十三研究所GaAs PHEMT 工艺线的模型进行功率放大器的设计,GaAs PHEMT 场效应管总栅宽1mm的输出功率为0.6 W,若需要输出33 dBm,即2W 功率,末级总栅宽需4mm,使用4个功率单元,每个单元总栅宽1 mm.要得到高效率的功率放大器,需要仔细考虑每一级场效应管的总栅宽比,可以达到最大效率。

根据设计目标确定相应的电路拓扑结构,拓扑结构的选择决定着整个电路的性能,对有源器件进行负载牵引,找出有源器件能够输出最大功率时的输入和输出阻抗在阻抗圆图上的位置。本文所用1 mm栅宽模型如图4 所示,图4(a)为模型版图形,用于进行器件建模,图4(b)为通过测量参数拟合的大信号模型。输出匹配网络的设计着眼于最大的功率输出,拓扑结构如图5所示。

APP下载

APP下载 登录

登录

热门文章

热门文章