虽然这是一个浮躁的社会,充满着一夜暴富的神话,但是学习技术真的很少存在所谓的捷径。这么说吧,至少贫僧还没有那个本事,完成“三周精通某某某”的本领。如果有听众还要速成,某家不得不说您老这票错了。小本经营,概不退票啊。急于见到代码的“傻弟弟”们,实际上属于信心缺失的毛病。和不做系统、结构设计就直接上coding一样,根本不是“艺高人胆大”,而是信心缺失。第一讲,施主没见到Verilog代码,这一讲里面状况虽然有所改善,但是也好不到那里去:您老还是别妄图做能综合或者仿真的代码,这个最少要等到下一讲。

关于Verilog语言的官方标准全称是《IEEE Std 1364-2001:IEEE Standard Verilog® Hardware Description Language》。其中包括27章以及8个附录,真正对于电路设计有用的内容大约1/3的样子。

Verilog是一种硬件编程语言,它既是一种结构描述的语言也是一种行为描述的语言,也就是说对于同一功能的物理电路,我们可以用Verilog中提供的数字电路中较为形象的门级结构来描述电路,也可以用更为抽象的一些语句来描述电路,于是乎,我们根据抽象的程度不同,将不同的描述方式进行划分,得到以下几种不同抽象级别的描述方式,其中,从上至下,离真相越来越近,也就是说最形象的是开关级,其次是门级,依次类推,最抽象的是系统级。

系统级(System Level):用高级语言结构实现设计模块的外部性能的模型;

算法级(Algorithm Level):用高级语言结构实现设计算法的模型;

RTL级(Register Transfer Level):描述数据在寄存器之间流动和如何处理这些数据的模型;

门级(Gate Level):描述逻辑门以及逻辑门之间的连接的模型;

开关级(Switch Level):描述器件中三极管和存储节点以及它们之间连接的模型。

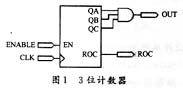

换言之,不同级别的抽象,也就是说在不同抽象层次上用Verilog语言来描述一个物理电路,若从行为和功能的角度来描述某一电路,则为行为级描述,系统级、算法级和RTL级属于行为级描述方式;若从电路的结构来描述某一电路,则为结构级描述,门级和开关级属于结构级描述方式。在实际应用中,我们要根据需求对每个Verilog模型进行设计,选用不同抽象级别的描述,才能使我们的设计事半功倍。各个层次的关系如图1所示。每个层次都可以单独进行设计,这个和练“龙象般若功”不同,无需按照等级一层一层玩。

图1 Verilog逻辑层次及其与工程阶段的关系

很多初学者感觉学习Verilog语言是老虎吃天----无从下口呢?这是和Verilog的贪心不足密切相关的。从工程方法学的角度上说,设计和验证是完全不同的两个行当,很少有人能够做到“昆乱不当”的。然而,Verilog标准里面,确实体现了完全的五味杂糅,认为的造成了混乱,这是所谓“困难”的源头。

本套数只会讲RTL的那些事儿,其他的内容请另找师傅吧,老衲不反对。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多