3.4.3随机采样

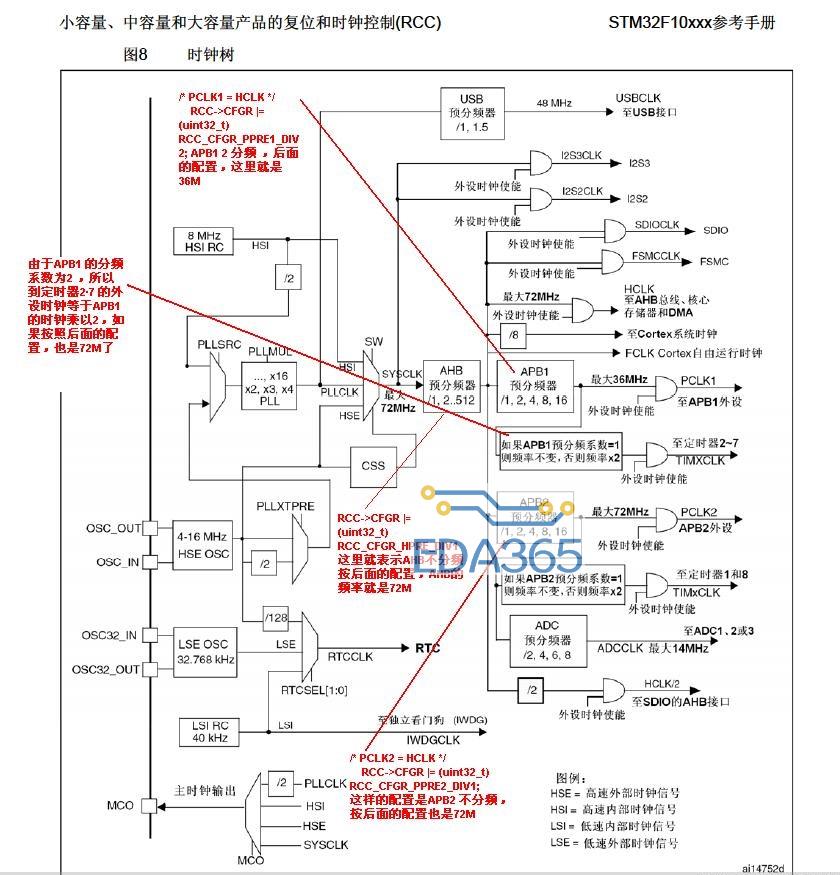

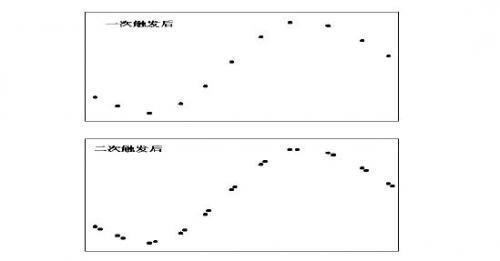

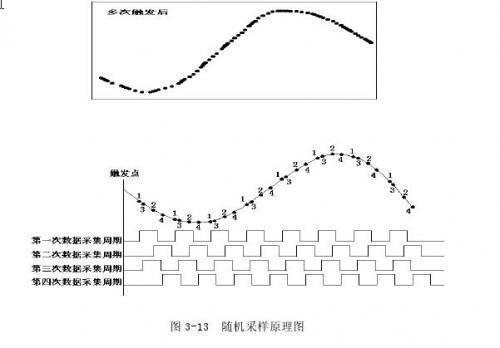

随机采样也是一种等效时间采样。它的采样点是在随机时刻采集的,与触发事件无关。这些采样点之间的时间间隔为一已知的时间,由采样时钟确定。当示波器在等待触发事件时,A/D就在连续的进行采样,并存入FIFO.当一个触发事件到来时,时间测量电路就对触发脉冲到触发脉冲后第一个采样脉冲之间的时间间隔进行测量。由于采样间隔是固定的,所以,示波器能得到相对位置固定的一组采样点。当第一次采集的所有采样点存储完毕之后,就开始采集一组新的采样点,并等待新的触发事件。新触发事件到来以后,时间测量电路又进行新的时间测量,以此来排列第一组采样点和第二组采样点的相对位置,并按顺序存入存储器。随机采样的原理图如图3-13.

顺序采样与随机采样都属于等效时间采样,在这两种取样方式下,示波器的带宽称为等效带宽。它们的共同之处是都只能观测周期信号。但同时它们也有很大的不同:1.顺序采样的采样点与触发脉冲有△t的延迟时间关系,而随机采样的采样点与触发脉冲无任何关系,完全是随机的。2.顺序采样触发后每个信号周期只有一个采样点,而随机采样每个信号周期可以获得一组采样点。在实际应用中,由于随机采样要计算摆点的位置,所以它填满一个完整的波形所花的时间要比顺序采样多一些,但随机采样相比于顺序采样最大的优点在于能够提供预触发信息。

1.随机采样的实现

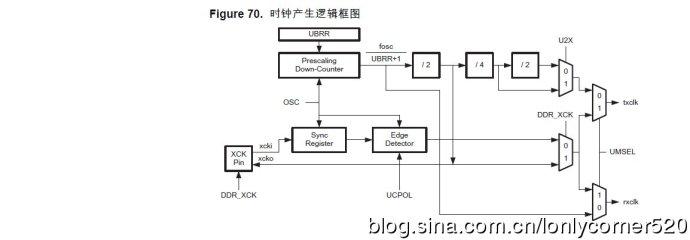

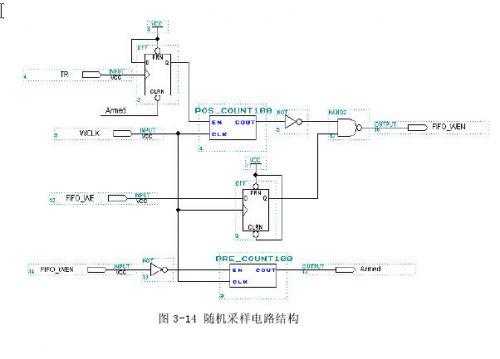

随机采样与实时采样的实现电路有所不同。实时采样的“+”延迟触发计数器和“—”延迟触发计数器是通过DSP来设置计数值,而随机采样我们是固定两个计数器的值为100,也就是说触发前和触发后各采100个点。随机采样的主要电路结构如图3-14.

首先,在每个写时钟(WCLK)检测DSP是否发出FIFO写使能信号(FIFO_WE)。当DSP发出写FIFO命令时,D触发器输出为“1”。同时,由于计数器POS_COUNT100初始时输出为“0”,所以经反相后输出为“1”,与D触发器的输出同作为与非门的输入,将FIFO写使能(FIFO_WEN)置为“0”。FIFO_WEN经反相后作为PRE_COUNT100的计数使能信号,计数器根据写时钟计数。当计满100个数后,Armed变为高电平,允许触发信号TR.等待触发过程中,FIFO写时钟等于FIFO读时钟。当触发脉冲到来时,FIFO读时钟无效,POS_COUNT100开始根据写时钟计数。计满100个数后POS_COUNT100输出变为“1”,使FIFO写使能无效,从而结束一次触发一组数据的采集。

2.时间测量电路

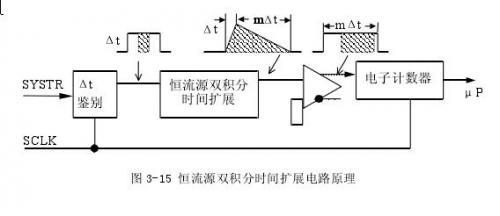

要实现随机采样技术,其关键就是要精确测量触发脉冲与触发脉冲后第一个采样脉冲之间的△t,只有准确的测量出这个△t才能摆正各次触发所采集的采样点在时间轴上的时间关系,从而保证正确的重现信号波形。

项目中,由于实时采样率为100MSPS,且触发脉冲和采样脉冲的出现在时间轴上具有随机性,因此,两者间的时间间隔△t很小(0≤△t<10nS),且为0至10nS区间的任意值,难于对其进行直接的测量和处理。间接测量的方法有多种,采用模拟时间扩展器测量第一采样脉冲与触发脉冲之间的随机时间间隔△t是一种可行的方案。我们采用的模拟扩展电路是恒流源双积分时间扩展电路,它将时间间隔△t线性放大数倍(通常放大倍率为250至500倍),形成计数时间闸门,在闸门时间内对标准时钟源T 0计数。然后根据计数结果确定△t的值。该功能单元的原理框图由图3-15所示。

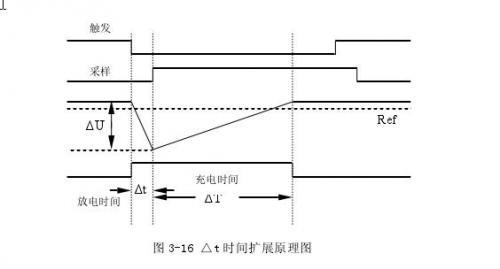

本系统采用的恒流源双积分时间扩展电路是利用两个恒流源对一个电容的快放慢充电,来实现对时间的展宽:在触发脉冲下降沿到来时进行放电,当第一个采样脉冲上升沿到来时进行充电,且放电电流远大于充电电流,就可以实现时间的展宽。图3-16为双斜率电容充电电路时间展宽工作原理示意图。

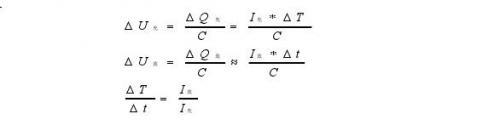

由图知,

即双斜率积分时间展宽电路的放大倍数是放电电流与充电电流之比。而实际电路的充放电流具有非线性,尤其对很小的时间间隔,非线性的影响就非常明显。另外充放电路输出的锯齿波,还要送到比较器以产生所需的计数时间闸门,所以实际的放大倍数小于理论计算出的放大倍数。

若DSO的最小时间分辨率tes =200ps,计数脉冲为To =10ns,则时间放大倍数是K:K= To/tes =50,因此双斜率积分时间展宽电路的实际放大倍数必须大于50倍。在保证充放电线性的基础上提高放大倍率显然有利于提高时间测量精度,放大倍率的调节可以通过调节充电电流和放电电流的大小实现,还可通过调节比较电压和电容值来实现微调。

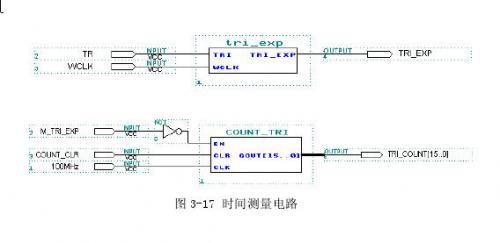

事实上,要让恒流源双积分时间扩展电路要工作***性区△t不能太小,而由上文分析知道0≤△t<10nS,且在[0,10nS)区间任意取值,这就必然导致有时模拟扩展器不能正常工作。为了解决这一矛盾,我们在△t上插入一个恒定的时间间隔T0(T0 =10nS),这样△t +T0∈[10 nS,20nS)。经过处理后的时间间隔就可以确保时间扩展器电路工作***性区。实现电路如图3-17所示。

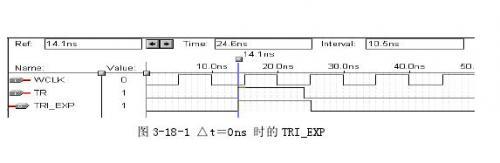

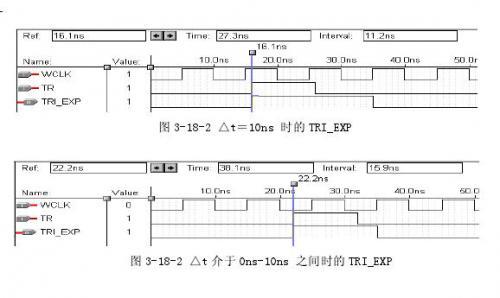

如图所示,TRI_EXP 模块主要完成△t+10ns 的功能,其仿真图如图 3-18。

COUNT_TRI 模块主要完成对模拟展宽后脉冲的计数工作。其中,M_TRI_EXP为模拟电路送来的展宽后脉冲所形成的闸门信号,用它来作为计数使能控制。同时,用 100MHz 时钟来对它进行计数。TRI_COUNT[15..0]为展宽脉冲的计数值,计数结束后将它送入 DSP,做为摆点的依据。

3.时间扩展器的校准

由于模拟脉冲展宽电路是由一些分离元件设计的,工作状态易受温度等外界环境因素影响,展宽倍数也因此随时在改变,所以很难精确的计算其展宽倍数。为了消除K值的变化、比较电平的漂移带来的误差,所以引入校正技术:通过三次测量,即先测To和2To的值,再测tx+To值进行计算处理。

(1)当t = T0时,扩展后得:NsT0=KT0-TH

计数值Ns=(KT0-TH)/TH (A)(其中,TH为无效扩展时间)

(2)当t = 2T0时,扩展后得:NsT0=2KT0-TH

计数值Nr=(KT0-TH)/TH (B)

(3)当t=tx+T0时,扩展后得:NsT0=K(tx+T0)-TH

计数值Nx=[(K(tx+T0)-TH)]/TH(C)

将式(B)减去式(A),得Nr-Ns=K

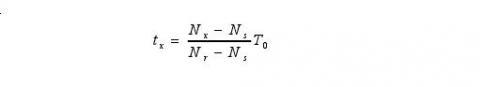

将式(C)减去式(A),得Nx-Ns=Ktx/T0,并将上面的K值带入,得:

由上式可见,通过对扩展器的校正,完全消除了恒流源和比较电平的变化对测量结果的影响。以上电路可以方便地在FPGA中实现。

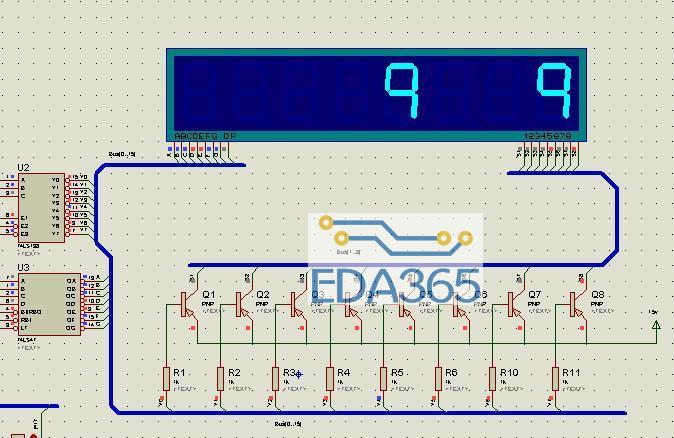

4.随机采样的显示

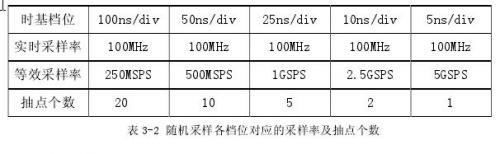

上面我们已经介绍过本项目中在100ns/div-5ns/div的档位下采用随机采样技术,而且随机采样的时候,我们的采样率固定为100MHz.我们知道示波器时间轴上共有10格,每格25个点。所以,当在5ns/div档位下的时候示波器的等效采样率最高,等于5GSPS(5ns/25 =0.2ns)。在具体实现随机显示的过程中,我们采用抽点显示的方法,即在等效采样率最高的时候,采样足够多的点,然后每个档位依此抽点显示。随机采样时,各档位的等效采样率以及抽点个数如表3-2.

APP下载

APP下载 登录

登录

热门文章

热门文章