当前最流行的硬件设计语言有两种,即 VHDL 与 Verilog HDL,两者各有优劣,也各有相当多的拥护者。VHDL 语言由美国军方所推出,最早通过国际电机工程师学会(IEEE)的标准,在北美及欧洲应用非常普遍。而 Verilog HDL 语言则由 Gateway 公司提出,这家公司辗转被Cadence所购并,并得到Synopsys的支持。在得到这两大 EDA 公司的支持后,也随后通过了 IEEE 标准,在美国、日本及中国台湾地区使用非常普遍。

我们把这两种语言具体比较下:

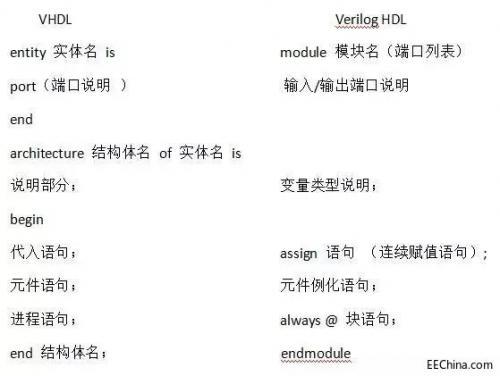

1.整体结构

点评:

两者结构基本相似,并行语句的种类也类似;

VHDL语言需要进行大量说明,程序通常比较长;

Verilog HDL通常不进行说明,或只进行非常简短的说明,程序比较简短。

2.数据对象及类型

VHDL

常量 信号 变量 9种预定义类型 各类用户定义类型

可描述各类不同的量

必须进行类型说明

运算时必须考虑类型的一致性和适用性

Verilog HDL

常量: 数量,参量

变量:网络型 寄存器型

类型种类少

运算时所受的约束少

3.运算符号

运算主要分为3类 : 算术运算 逻辑运算 关系运算

算术运算

VHDL中有10种 但很多都不能进行综合,只能用于行为描述

Verilog HDL中只有能够综合的5种

逻辑运算

VHDL中 有常用的6种,均用字符形式表达

Verilog HDL中有3类共14种,

分为一般逻辑运算,位逻辑运算,缩减逻辑运算

关系运算

VHDL中有6种

Verilog HDL中有2类共8种,对比增加了全等和不全等(用于对不定态比较)。

除了以上3类运算外,VHDL中还有连接运算,Verilog HDL中还有连接运算、移位运算和条件运算。

点评:

VHDL的运算划分比较抽象,适应面较广

Verilog HDL的运算划分比较具体,对逻辑代数反映更细致一些。

4.语句

两种语言的语句都分为并行语句和顺序语句,并行语句在主程序中使用,顺序语句只能在子结构中使用;

并行语句都分为3种形式:

APP下载

APP下载 登录

登录

热门文章

热门文章