使用WinPcap 自定义通信帧格式,实现一种PC 机与FPGA 之间双向高速数据传输的方法,绕过TCP 协议和IP 协议,只涉及到链路层和物理层,降低了FPGA 端的协议解析复杂度、减少拆包时间和时延,且突发速率达到1Gbit /s。

近年来,FPGA( Field Programable GateArray,现场可编辑门阵列) 在通信领域的应用越来越广泛,FPGA 运行速度快,容易实现大规模系统,内部程序并行运行,但进行高精度复杂运算处理是FPGA 的劣势,同时由于计算机具有强大的运算和处理能力,可以将高精度复杂运算由PC 机完成后再交由FPGA完成其他工作。千兆以太网作为一种高速以太网技术,仍采用了与10M 以太网相同的帧格式、帧结构、网络协议、全/半双工工作方式、流控模式以及布线系统。利用千兆以太网,可以方便地构建PC机与FPGA 的高速数据传输系统。

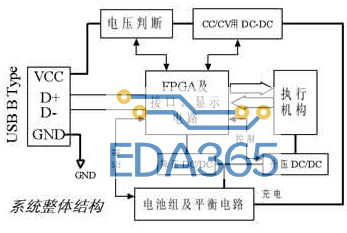

系统总体设计如图1 所示,数据通过PC 机的网卡发送,利用千兆以太网作为传输媒介,传输至FPGA 端时首先通过SFP 光模块进行电光转换,然后到达FPGA 的Rocket-IO PHY 层,该层是高速的串行收发器,可对数据进行单工或双工的收发。接收完成的数据被送至MAC 层进行地址解析与校验,只有当解析与校验结果正确且FIFO 不满时,数据才能被写入FIFO。写入FIFO 的数据可被后续的用户逻辑进行相关的数据处理。

在PC 端,考虑到所传输数据具有较为固定的格式且传输速率很高,将不采用传统的套接字服务( SOCKET) ,改为在Winpcap 驱动基础上构造并发送或接收自定义的数据包格式。该数据包格式对传统的以太网数据包格式进行大量简化,绕过TCP 和IP 协议,只设计数据链路层与物理层,降低FPGA 端协议解析的复杂度,减少拆包时间与时延。

1.1 Winpcap 简介

WinPcap 是应用于Win32 平台的数据包捕获与网络分析的一种体系结构,为Win32 应用程序提供访问网络底层的能力,其主要思想来源于Unix 系统中BSD 包捕获构架。WinPcap 主要由3 个模块组成:

( 1) NPF 包过滤器,数据包监听设备驱动程序,是架构的核心,它工作在内核级,主要功能是过滤数据包。它直接从数据链路层取得网络数据包,不加修改地传给运行在用户层的应用程序,也允许用户发送原始数据包。

( 2) Packet.dll 是低级的动态链接库,运行在用户级,把应用程序和数据包监听设备驱动隔离开来,使得程序可以不加修改地在不同的Windows 系统上运行。通过Packet. dll 提供的能用来直接访问BPF驱动程序的包驱动API,利用“raw”模式发送和接收包。不同Windows 系统上的Packet. dll 并不相同,但由于它提供了一套相同的调用接口,这样使得高级系统无关库不依赖于特定的Windows 平台。

( 3) Wpcap. dll 是高级系统无关库,也工作在用户级,它和应用程序编译在一起,并使用低级动态连接库Packet. dll 提供的服务,向应用程序提供完善的监听接口。

由于WinPcap 的主要功能在于独立于主机协议( 如TCP /IP) 来发送和接收原始数据包。即WinPcap 不能阻塞、过滤或者控制其他应用程序数据包的发送,它仅仅只是监听共享网络上传送的数据包。利用WinPcap 驱动程序发出的数据包将不含有IP头和TCP 头,只含有MAC 地址和数据,简化了硬件上的数据帧格式解析。

1. 2 自定义数据帧格式

以太网可以工作在10Mb /s,100Mb /s,1Gb /s等,同时它可以工作于多种传输媒体下,但是所有类型的以太网都有一个统一的帧结构。前导码( 7 字节) 、帧起始定界符( 1 字节) 、目的MAC 地址( 6 字节) 、源MAC 地址( 6 字节) 、类型/长度( 2 字节) 、数据( 46 ~ 1500 字节) 、帧校验序列( 4 字节) 。

如PC 机端使用普通的网口编程方法,会带有IP 头和TCP 头等,给FPGA 端拆包、协议解析带来复杂度。为此采用WinPcap 驱动编程,实现FPGA与PC 网口之间的自定义数据帧格式,使FPGA 端接收到得数据帧格式为类似802. 3 协议的以太网数据包格式,但不会含有IP 头和TCP 头等协议开销,具体如表1 所示。

其中,控制标志用于对FPGA 的寄存器进行设置控制; 校验同标准100Base - T 帧的FCS 域,内容为32bit 的CRC 检验值,检验范围包括目的地址、源地址、控制、信息数据4 个字段。

对以太网进行CRC 运算的数据是并行输入的,要根据PC 上( Windows 操作系统环境) 数据的组织方式对余数进行调整,如果是Big Endian 的组织方式则将余数按位取反得到CRC 数据,如果是Little Endian 的数据组织方式则先要将余数进行位置互换,然后再按位取反。本设计中是Big Endian 的组织方式。

PC 端收发网口数据时,前导码、界定符、帧校验3 项由网卡自动处理。FPGA 端处理网口数据,则要按以上帧格式处理。

在PC 端,软件的编写基于Winpcap 驱动程序。本设计中使用的是Winpcap3. 1 版本,在安装好驱动程序WinPcap_3_1. exe 后,解压缩WpdPack_3_1. zip文件至一自定义目录,现假设为D: \ wpdpack_3 _1下,然后将其中lib 文件下的wpcap. lib 文件复制到所建的工程目录下。

在VC2005 工程属性下,打开C + + 选项,在附加包含目录中,添加刚才WpdPack_3_1. zip解压目录路径,现为d: \wpdpack_3_1 \WpdPack\Include; 在链接器选项中,在输入的附加依赖项中添加wpcap. lib。然后,在需要调用winpcap 函数的CPP 文件的开头,添加#include “ pcap. h”。数据包发送与接收流程如图2 所示。

FPGA 硬件部分采用Xilinx 公司的V5 系列芯片,基于VHDL 硬件描述语言实现。V5 芯片内嵌Tri-mode Ethernet Media Access Controller 硬核,该硬核与RocketIO 联合可以1000Base-X ( 即1000Base-X PCS /PMA) 。

1000BASE-X 物理标准被定义为与一个光学结构媒介相连接的物理子层。当前存在的两种常见方式: 1000BASE-LX 和1000BASE-SX( 长波和短波激光) ,它们都可以通过将RocketIO 连续收发器与适当的GBIC 或SFP 光学收发器相连来得到。本设计采用SFP 与RocketIO 相连接的方案,数据从PC 端网口通过千兆以太网送至SFP 光模块,然后达到FPGA 的RocketIO 模块。

RocketIO 是一种高速的串行收发器,采用两对差分对来进行数据的发送和接收,可以实现两个单工或一对全双工的数据传输。RocketIO 包括PMA( Physical Media Attachment,物理媒介适配层) 和PCS( Physical Coding Sublayer,物理编码子层) 两个子层。其中,PMA 子层主要用于串行化和解串,PCS主要包括线路编码和CRC 校验编码。

MAC 层首先完成源地址和目的地址的解析,并开始对自定义格式的数据帧中相关字段进行CRC校验,若地址正确则输出数据写使能信号,数据加载至FIFO 模块。只有当写使能被声明且FIFO 不满时,数据才从输入bus( DIN) 加载,同时写应答( WR_ACK) 被声明。

FPGA 接收时序如图3 所示。

发送过程是接收过程的逆过程,按自定义的数据帧格式封装数据,只是注意要将最后一个字节的数据校验完后把余数位取反得到CRC 数据,这里不再赘述。

本设计用于一种脉冲雷达通信系统中,实现了PC 机和FPGA 之间的双向高速数据传输,且突发速率达到1Gbit /s。由于采用了自定义的类似802.3协议的以太网数据包格式,有效降低了协议复杂度,且减少了分组包头开销和时延。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多