如今我们缺乏一种全面准确评估芯片制造影响的方法。近日,Imec制定了一个解决方案,通过扩展其设计-技术协同优化(DTCO)框架,可以估计当前和未来的逻辑CMOS技术的能源消耗、水资源使用和温室气体排放的状况。第一个分析显示,由于芯片技术日益复杂,节点之间的所有这些指标都在增加。该框架会让企业做出更加符合可持续的制造方针。

如何保障半导体的环境可持续性

半导体产业是涵盖能源、水、化工和原材料的资源密集型产业。在生产过程中,会产生不同种类的排放物,包括二氧化碳和氟化化合物等温室气体。为了最大限度地减少行业对环境的影响,并遵守当地和全球的政策,环境、健康和安全(EHS)控制这些因素已经成为每一个代工厂关键考虑的部分。

但由于对气候变化、资源消耗和全球污染的日益关注,晶圆厂和设备供应商希望在绿色集成电路制造方面做出更多努力。虽然EHS控制主要局限于化学品、减排和水管理,但电子公司希望了解并减少其产品的全部碳足迹。减少碳足迹也能保证业务的连续性。今天,公司依靠生命周期评估(LCA)等方法来评估其产品从原材料采购到寿命结束的环境影响。

未来集成电路的生命周期评估

然而,目前的LCA方法还远远不够精确和完整,特别是在集成电路方面。最新发布的关于芯片制造中使用的质量平衡和能量流的信息涉及到32nm技术节点——一项在2010年成为主流的技术。关于当前和即将到来的CMOS技术处理的环境数据是很难得到的。而我们所知道的大多来自于片面的观点,要么来自于设备或材料供应商,要么来自于代工厂在生产后发布的内容。无晶圆厂的公司根本无法获取信息。缺乏一种整体的方法,使得将环境考虑因素纳入早期技术确定阶段极具挑战性。

主要障碍:未来技术日益复杂

由于节点间复杂度的增加,预计CMOS技术对环境的影响将变得非常复杂。多年来,在芯片制造的所有步骤——包括前端生产线(FEOL)、中间生产线(MOL)和后端生产线(BEOL),都引入了新的材料、设备结构、工艺和设备,以确保摩尔定律的连续性。对于未来的节点,我们也在探索新方法,以进一步减少逻辑单元面积,同时提高节点之间的性能(即操作频率)。

为了设计更加紧凑的间距,光刻技术已经从单曝光193nm发展到双曝光、三曝光或四曝光方法。EUV光刻可用于7nm节点,大大减少工艺步骤的数量。但并不是每家代工厂都能实现了这一转变,因为同一种间距有多种加工路线可供选择。对于未来的技术节点,将需要多个EUV光刻序列来印刷30nm以下的pitches。

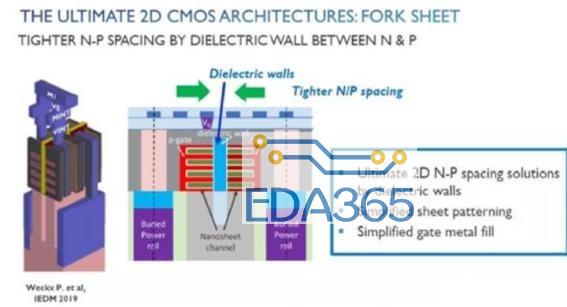

在FEOL中,FinFET已经成为7nm技术节点的主流设备架构,7nm技术节点是目前芯片生产中使用的最先进节点。对于下一个技术节点,imec认为(垂直堆叠)横向纳米片是未来的发展方向,其次是Forksheet结构和综合性互补FET(Complementary FET,CFET)。

对于Complementary FET(CFET)而言,它是在1nm节点采用的方法。在此,通过在p型FET上堆叠n型FET,即通过三维堆叠具有不同导电类型的晶体管,从而标准单元面积被大大减小。据说芯片的背面可以提供更多功能,但未公开细节。从这里开始,将采用high-NA EUV光刻以进一步微缩晶体管结构。

IMEC还希望采用二维材料,自旋电子学和量子计算。为了将来进一步微缩,除了设计和工艺协同优化(DTCO)之外,系统和工艺协同优化(STCO)也很重要。

为了跟上前端面积的缩放,BEOL尺寸急剧减小——这导致金属节变得越来越小,导线的截面面积也越来越小。这些年,互连层的数量和最密集的金属线复杂性已经显著增加。人们正在探索新的金属化工艺方案,并正在引入新的金属来降低最致密层的电阻率。

设计-技术协同优化DTCO

伴随着这种演变出现了DTCO——设计-技术联合优化。2005年以前,半导体的技术演进很顺利,处于“happy scaling”时代。不断缩小的晶体管在功耗、性能、面积和制造成本(表示为PPAC)方面为整个系统带来了好处。但自2005年以来,人们逐渐意识到,只有在设备技术和设计共同优化的情况下,才能保持这些好处。DTCO通过引入缩放助推器,允许进一步缩小面积,但这不是在晶体管上,而是在标准单元水平上。缩放助推器,如自对准栅触点或埋置功率轨,进一步改善了芯片不同部分之间的连接,但也影响了FEOL、BEOL和MOL水平上的芯片生产。

DTCO的可持续性发展

DTCO框架可以作为分析环境指标的基础,这些环境指标可以与标准PPAC指标并行监测。DTCO考虑了当前和未来集成电路技术的工艺流程。这些可以与工艺步骤和设备的相关环境信息相结合,允许进行电能-性能-区域-成本-环境(PPACE)的分析。

Imec将电能消耗、超纯水使用和温室气体排放作为评估环境影响的主要指标。为了利用这些指标扩展DTCO框架,imec团队使用了来自其300mm fab的数据,并补充了来自其设备供应商生态系统的信息。通过这种方式,不同的知识可以被连接起来。

这样做的目的是在不同的缩放选择上进行PPACE分析,以识别大批量制造之前的瓶颈、风险和机会。要进行正确的评价,需要一个真正的整体方法。例如,极紫外光刻工具比传统的193nm(浸入式)光刻工具消耗大约10倍的功率。但EUV也将显著减少处理步骤的数量,这是在推导总能耗时必须考虑的因素。

Imec使用扩展的DTCO框架对不同的工艺流程和集成方案进行量化和基准测试,从28nm到2nm节点。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多