半导体产业抵达10纳米制程的路途漫长而艰辛,但英特尔(Intel)似乎找到如何发挥这个制程优点的方式,即将发布的首个Cannon Lake笔记型电脑(NB)料将展现成果。

英特尔继3年前在国际电子元件大会(IEDM)大会发布14纳米技术,近一年前在CES中展示Cannon Lake NB之后,英特尔在2017年的IEDM中首次开始公开说明10纳米制程细节,并且展示面积1平方厘米晶粒范围内封装1亿颗电晶体的成果,宣称是迄今密度最高的CMOS电晶体。

英特尔年初在Technology and Manufacturing Day曾说明10纳米技术的基本功能,此制程鳍片的间距为34纳米,闸极间距为54纳米,最小的金属间距为36纳米。英特尔自从180纳米之后即持续将每个世代的SRAM单元体积缩小0.5倍,10纳米为0.0312平方微米。这样的尺寸类似晶圆厂为苹果(Apple)、NVIDIA和高通(Qualcomm)以7纳米制程制造的芯片。

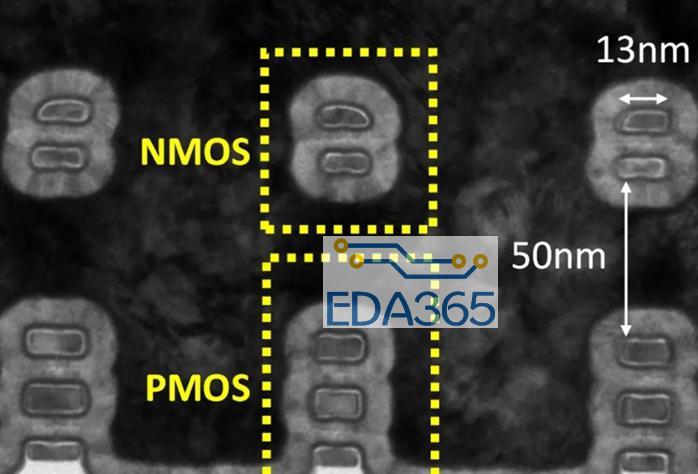

英特尔这次在IEDM上提供更多制造步骤、功能和材料细节。10纳米制程采用英特尔第3代3D鳍式电晶体(FinFET),当鳍片更薄、更高时,性能也会更佳,10纳米制程的鳍片宽度只有7纳米,高度46纳米(先前英特尔曾提到是53纳米),高度可以随着不同的应用而调整,缩放范围是5纳米。

英特尔微缩制程的标准193纳米浸润式微影(immersion lithography)工具是采用所谓的自对准四重图案(Self-Aligned Quadruple Patterning;SAQP) 来制造鳍片,过程增加四个额外的步骤来提高密度。英特尔还在标准单元(cell)中减少鳍片数量,同时引用两种新技巧来增加密度。第一个是消除边界主动式单元的假性闸极(dummy gate),另外一个是有源闸极上接触(contact-over-active-gate,COAG),将介层(via)直接置入主动式闸极区,这需要三个额外的步骤,单元面积则缩小10%。

按照英特尔的估算方式,英特尔的密度有加速提升的趋势,从45纳米到22纳米的2倍,到14纳米和10纳米时提高为2.7倍。不过,英特尔似乎计划进一步加快速度,该公司Technology and Manufacturing Group副总裁Chris Auth透露,未来每两年晶粒的密度将会增加1倍。

随着鳍片间距缩小,接触到的电阻较低,英特尔最新制程的电晶体的性能进一步提升,先前曾表示相较于14纳米,10纳米性能将增加25%,消耗电力减少近一半。但在IEDM上英特尔表示,10纳米驱动电流比NMOS电晶体增加71%,比PMOS增加35%。

英特尔并未说第一个10纳米处理器何时推出,但首个家族成员Cannon Lake可能2018年出现在笔记型电脑之中。

关键字:英特尔 IEDM『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多